# Complete Formal Hardware Verification of Interfaces for a FlexRay-like Bus

Dissertation

zur Erlangung des Grades Doktor der Ingenieurswissenschaften (Dr.-Ing.) der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

Christian Müller

Saarbrücken, November 2011

Tag des Kolloquiums:7. November 2011Dekan:Prof. Dr. Holger HermannsVorsitzender des Prüfungsausschusses:Prof. Dr. Philipp Slusallek1. Berichterstatter:Prof. Dr. Wolfgang J. Paul2. Berichterstatter:Dr. habil. Silvia Melitta MüllerIBM Systems & Technology GroupIBM DeutschlandAkademischer Mitarbeiter:Dr. Gordon Fraser

Hiermit erkläre ich, dass ich die vorliegende Arbeit ohne unzulässige Hilfe Dritter und ohne Benutzung anderer als der angegebenen Hilfsmittel angefertigt habe. Die aus anderen Quellen oder indirekt übernommenen Daten und Konzepte sind unter Angabe der Quelle gekennzeichnet. Die Arbeit wurde bisher weder im In- noch im Ausland in gleicher oder ähnlicher Form in anderen Prüfungsverfahren vorgelegt.

Saarbrücken, November 2011

"Time turns the improbable into the inevitable."

Author unknown

## Acknowledgments

I owe my gratitude to Professor Paul for being a great teacher. I thank Ulan for all the adventures we have gone through. I thank Dr. Silvia Melitta Müller who kindly agreed to review this thesis.

#### Abstract

We report in this thesis the first complete formal verification of a bus interface at the gate and register level. The presented bus interface allows to implement a timetriggered system consisting of several units interconnected by a bus. Time-triggered systems work decentralized, allow some grade of fault-tolerance against a bounded number of single errors and show a predictable recurrent behaviour.

We use a hardware model for multiple clock domains obtained by formalization of data sheets for hardware components, and we review known results and proof techniques about the essential components of such bus interfaces: among others serial interfaces, clock synchronization and bus control. Combining such results into a single proof leads to an amazingly subtle theory about the realization of direct connections between units (as assumed in existing correctness proofs for components of interfaces) by properly controlled time-triggered buses. It also requires an induction arguing simultaneously about bit transmission across clock domains, clock synchronization and bus control.<sup>1</sup>

The design of the bus controller can be automatically translated into Verilog and deployed on FPGAs.

#### Zusammenfassung

In dieser Arbeit präsentieren wir die erste formale Verifikation einer Bus-Schnittstelle auf der Register- und Gatter-Ebene. Die Bus-Schnittstelle ermöglicht die Implementierung eines zeitgesteuerten Systems, welches aus mehreren Einheiten besteht, die durch einen Bus verbunden sind. Systeme dieser Art funktionieren dezentralisiert, sind fehlertolerant gegen einzelne System- und Umgebungsfehler und weisen ein berechenbares periodisches Verhalten auf.

Wir benutzten ein Hardware-Model für mehrere Clock-Domänen, welches durch die Formalisierung der Herstellungsinformationen abgeleitet wurde. Wir präsentieren verschiedene Ergebnisse und Verifikationstechniken über die essentiellen Komponenten solcher Bus-Schnittstellen: serielle Schnittstellen, Clock-Synchronisierung, Bus-Kontrolle, usw.

Die Kombination solcher Ergebnisse zu einem einzigen Korrektheitsbeweis führt zu einer nicht-triviallen Theorie über die Realisierung einer direkten Verbindung zwischen verschiedenen Einheiten des Systems (wie das in den einzelnen Beweisen verschiedener Komponente angenommen wird), die auf einer korrekten Kontrolle zeitgesteuerter Busse basiert. Die Korrektheit der gesamten Schnittstelle ergibt sich aus einem Induktionsbeweis, der gleichzeitig über drei Eigenschaften argumentiert: über die Signalübertragung zwischen unterschiedlichen Clock-Domänen, über die Clock-Synchronisierung und über die zeitlich-korrekte Einteilung der Bus-Zugriffe.

Die Implementierung kann automatisch in Verilog-Code übersetzt werden und auf FPGA-Boards ausgeführt werden.

<sup>&</sup>lt;sup>1</sup>Note that this abstract partially coincides with the abstract of [PM11].

# CONTENTS

| 1.2 The Problem         1.3 Related Work         1.4 Contribution to the "Automotive" Project         1.5 Tools         1.6 Outline         2 Basics         2.1 Notation         2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits         2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3.1 Formalization of Clocks         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.3 Digital Signal Transmission Across Different Clock Domains .                                                                                    | 1 | Int | roduction                                                         | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------------------------------------------------------------------|----|

| 1.3 Related Work         1.4 Contribution to the "Automotive" Project         1.5 Tools         1.6 Outline         2 Basics         2.1 Notation         2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits         2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.3.3 Clocks and Clock Drift         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.3 Digital Signal Transmission Across Different Clock Domains .                                                                                                               |   | 1.1 | Motivation                                                        | 3  |

| 1.4 Contribution to the "Automotive" Project         1.5 Tools         1.6 Outline         1.6 Outline         2 Basics         2.1 Notation         2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits         2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2 Communication Scheme         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3 Clocks and Clock Drift         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.3 Digital Signal Transmission Across Different Clock Domains .                                                                                     |   | 1.2 | The Problem                                                       | 4  |

| 1.5 Tools       1.6 Outline         1.6 Outline       1.6 Outline         2 Basics       2.1 Notation         2.1 Notation       2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits       2.3 Boolean Gates and Basic Circuits         2.4 Terminology       2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2 Communication Scheme         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3 Clocks and Clock Drift         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.3 Digital Signal Transmission Across Different Clock Domains .         4.3.4 Improvement of Theorem 1 |   | 1.3 | Related Work                                                      | 6  |

| 1.6 Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 1.4 | Contribution to the "Automotive" Project                          | 9  |

| 2 Basics         2.1 Notation         2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits         2.4 Terminology         2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2 Communication Scheme         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3 Clocks and Clock Drift         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.4 Improvement of Theorem 1                                                                                                                                                                                                                |   | 1.5 | Tools                                                             | 10 |

| 2.1 Notation         2.2 Trace Semantics         2.3 Boolean Gates and Basic Circuits         2.4 Terminology         2.4 Terminology         3 Communication Model of a Simple FlexRay-like Time-Triggered Butem         3.1 Top Level Overview         3.2 Communication Scheme         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3 Clocks and Clock Drift         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.4 Improvement of Theorem 1                                                                                                                                                                                                                                                                                       |   | 1.6 | Outline                                                           | 10 |

| <ul> <li>2.2 Trace Semantics</li> <li>2.3 Boolean Gates and Basic Circuits</li> <li>2.4 Terminology</li> <li>3 Communication Model of a Simple FlexRay-like Time-Triggered Butem</li> <li>3.1 Top Level Overview</li> <li>3.2 Communication Scheme</li> <li>3.2.1 Time Notion of an ECU</li> <li>3.2.2 Synchronization</li> <li>3.3 Clocks and Clock Drift</li> <li>3.3.1 Formalization of Clocks</li> <li>3.3.2 Bounded Clock Drift</li> <li>3.4 Formalization of the Notion of Local Time</li> <li>4.1 Hardware Interconnection</li> <li>4.2 Detailed Register Model (DRM)</li> <li>4.3 Clock Domain Crossing Communication</li> <li>4.3.1 Transmission Correctness Across Two DRM Registers</li> <li>4.3.2 Improvement of Lemma 8</li> <li>4.3.4 Improvement of Theorem 1</li> </ul>                                                                                                                                                                                                                                                                                                           | 2 | Bas | sics                                                              | 13 |

| <ul> <li>2.3 Boolean Gates and Basic Circuits</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 2.1 | Notation                                                          | 13 |

| <ul> <li>2.4 Terminology</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 2.2 | Trace Semantics                                                   | 14 |

| <ul> <li>3 Communication Model of a Simple FlexRay-like Time-Triggered Butem</li> <li>3.1 Top Level Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 2.3 | Boolean Gates and Basic Circuits                                  | 15 |

| tem         3.1 Top Level Overview         3.2 Communication Scheme         3.2.1 Time Notion of an ECU         3.2.2 Synchronization         3.3.2 Synchronization         3.3 Clocks and Clock Drift         3.3.1 Formalization of Clocks         3.3.2 Bounded Clock Drift         3.3.4 Formalization of the Notion of Local Time         3.4 Formalization of the Notion of Local Time         4 Bus Model for Clock Domain Crossing Communication         4.1 Hardware Interconnection         4.2 Detailed Register Model (DRM)         4.3 Clock Domain Crossing Signal Transmission         4.3.1 Transmission Correctness Across Two DRM Registers         4.3.2 Improvement of Lemma 8         4.3.3 Digital Signal Transmission Across Different Clock Domains .         4.3.4 Improvement of Theorem 1                                                                                                                                                                                                                                                                              |   | 2.4 | Terminology                                                       | 17 |

| <ul> <li>3.1 Top Level Overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3 | Cor | nmunication Model of a Simple FlexRay-like Time-Triggered Bus Sys | -  |

| <ul> <li>3.2 Communication Scheme</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | tem | 1                                                                 | 19 |

| <ul> <li>3.2.1 Time Notion of an ECU</li> <li>3.2.2 Synchronization</li> <li>3.3 Clocks and Clock Drift</li> <li>3.3.1 Formalization of Clocks</li> <li>3.3.2 Bounded Clock Drift</li> <li>3.4 Formalization of the Notion of Local Time</li> <li>3.4 Formalization of the Notion of Local Time</li> <li>4 Bus Model for Clock Domain Crossing Communication</li> <li>4.1 Hardware Interconnection</li> <li>4.2 Detailed Register Model (DRM)</li> <li>4.3 Clock Domain Crossing Signal Transmission</li> <li>4.3.1 Transmission Correctness Across Two DRM Registers</li> <li>4.3.2 Improvement of Lemma 8</li> <li>4.3.3 Digital Signal Transmission Across Different Clock Domains</li> <li>4.3.4 Improvement of Theorem 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                          |   | 3.1 | Top Level Overview                                                | 19 |

| 3.2.2 Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3.2 | Communication Scheme                                              | 20 |

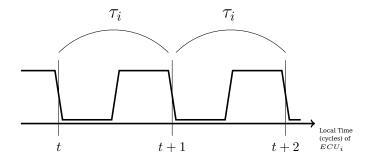

| <ul> <li>3.3 Clocks and Clock Drift</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     | 3.2.1 Time Notion of an ECU                                       | 21 |

| 3.3.1 Formalization of Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     | 3.2.2 Synchronization                                             | 21 |

| 3.3.2 Bounded Clock Drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3.3 | Clocks and Clock Drift                                            | 22 |

| 3.4       Formalization of the Notion of Local Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |     |                                                                   | 23 |

| 4       Bus Model for Clock Domain Crossing Communication         4.1       Hardware Interconnection         4.2       Detailed Register Model (DRM)         4.3       Clock Domain Crossing Signal Transmission         4.3.1       Transmission Correctness Across Two DRM Registers         4.3.2       Improvement of Lemma 8         4.3.3       Digital Signal Transmission Across Different Clock Domains         4.3.4       Improvement of Theorem 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |     | 3.3.2 Bounded Clock Drift                                         | 24 |

| <ul> <li>4.1 Hardware Interconnection</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 3.4 | Formalization of the Notion of Local Time                         | 26 |

| <ul> <li>4.2 Detailed Register Model (DRM)</li> <li>4.3 Clock Domain Crossing Signal Transmission</li> <li>4.3.1 Transmission Correctness Across Two DRM Registers</li> <li>4.3.2 Improvement of Lemma 8</li> <li>4.3.3 Digital Signal Transmission Across Different Clock Domains</li> <li>4.3.4 Improvement of Theorem 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4 | Bus | s Model for Clock Domain Crossing Communication                   | 31 |

| <ul> <li>4.3 Clock Domain Crossing Signal Transmission</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 4.1 | Hardware Interconnection                                          | 31 |

| <ul> <li>4.3.1 Transmission Correctness Across Two DRM Registers</li> <li>4.3.2 Improvement of Lemma 8</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 4.2 | Detailed Register Model (DRM)                                     | 33 |

| <ul> <li>4.3.2 Improvement of Lemma 8</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.3 | Clock Domain Crossing Signal Transmission                         | 36 |

| <ul><li>4.3.3 Digital Signal Transmission Across Different Clock Domains</li><li>4.3.4 Improvement of Theorem 1</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |     | 4.3.1 Transmission Correctness Across Two DRM Registers           | 38 |

| 4.3.4 Improvement of Theorem 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |     | 4.3.2 Improvement of Lemma 8                                      | 41 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |     | 4.3.3 Digital Signal Transmission Across Different Clock Domains  | 42 |

| 4.4 Extension to Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |     |                                                                   | 43 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 4.4 | Extension to Bus                                                  | 46 |

| 5  | ······································                            | 49  |

|----|-------------------------------------------------------------------|-----|

|    | 5.1 Correctness Statement                                         |     |

|    | 5.2 Low-Level Transmission Correctness                            | 50  |

|    | 5.3 Bus Control Correctness                                       |     |

|    | 5.4 High-Level Transmission Correctness                           | 52  |

| 6  | Bus Controller Implementation                                     | 53  |

|    | 6.1 Distributed Computation Model                                 | 54  |

|    | 6.2 ECU Computation Model                                         |     |

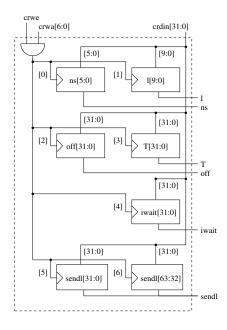

|    | 6.3 ECU Datapaths                                                 |     |

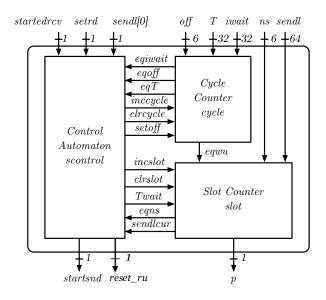

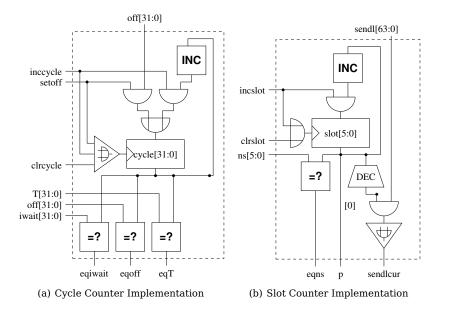

|    | 6.4 Scheduling And Clock Synchronization Protocols Implementation |     |

|    | 6.4.1 Configuration Registers Module                              |     |

|    | 6.4.2 Scheduler Module                                            |     |

|    | 6.5 Message Protocol                                              |     |

|    | 6.5.1 Send Unit                                                   |     |

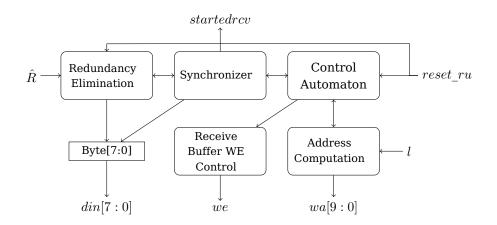

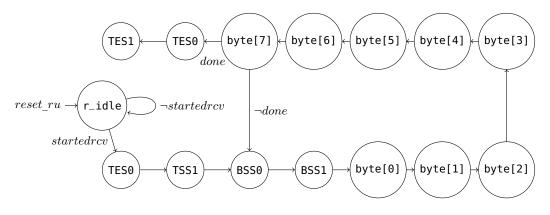

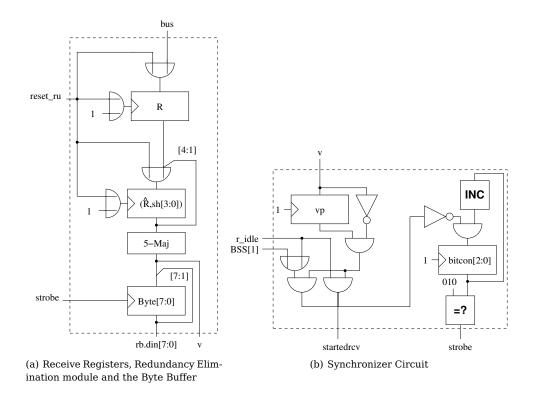

|    | 6.5.2 Receive Unit                                                |     |

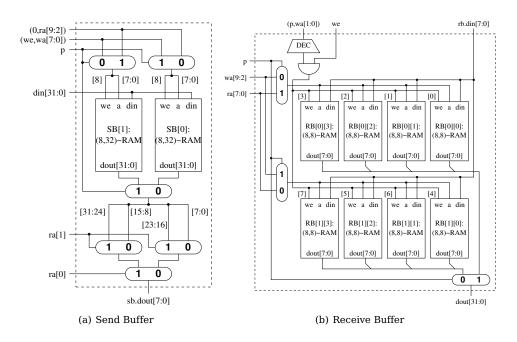

|    | 6.5.3 Send and Receive Buffers                                    |     |

|    | 6.6 Deploying on FPGAs                                            |     |

| 7  | Verification of Bus Contention Control                            | 71  |

| '  | 7.1 Previous Results and Their Improvements                       |     |

|    | 7.1.1 Synchronization Correctness                                 |     |

|    | 7.1.2 Schedule Execution Correctness                              |     |

|    | 7.1.3 Schedule Timing Correctness                                 |     |

|    | 7.1.4 Schedule Timing Correctness (Improved)                      |     |

|    | 7.2 From Local to Global Computational Semantics                  |     |

|    | 7.3 Startup Correctness                                           |     |

|    | 7.4 Schedule Correctness Of Master for All Rounds                 |     |

|    | 7.5 Schedule Correctness Of A Slave for All Rounds                |     |

|    | 7.5.1 Analog Output of a Receiver                                 |     |

|    | 7.5.2 Post-round Correctness of Analog Send Register Outputs      |     |

|    | 7.6 Bus Control Correctness                                       |     |

| 8  | Verification of Message Transmission                              | 105 |

|    |                                                                   |     |

| 9  | Conclusion                                                        | 111 |

|    | 9.1 Summary                                                       |     |

|    | 9.2 Discussion                                                    |     |

|    | 9.2.1 Tools                                                       |     |

|    | 9.2.2 Found Bugs                                                  |     |

|    | 9.3 Future Work                                                   | 113 |

| Aj | ppendix                                                           | 119 |

# LIST OF FIGURES

| 1.1 | Time-Triggered Bus System                         | 4  |

|-----|---------------------------------------------------|----|

| 1.2 | Decomposition of the Message Exchange Correctness | 5  |

| 1.3 | Direct Connection of Serial Interfaces            | 9  |

| 2.1 | Boolean Gates and Circuits                        | 6  |

| 3.1 | Network Topology of the Studied Bus Architecture  | 20 |

|     |                                                   | 21 |

| 3.3 | Local Time Notions of Different ECUs 2            | 21 |

| 3.4 | Overlapping Time Notions of Different ECUs        | 2  |

|     |                                                   | 23 |

|     |                                                   | 24 |

|     |                                                   | 27 |

|     |                                                   | 27 |

| 4.1 | Connection of an ECU to the Bus                   | 32 |

| 4.2 |                                                   | 33 |

| 4.3 |                                                   | 87 |

| 4.4 | 5                                                 | 37 |

|     |                                                   | 0  |

| 5.1 | Schematic Message Transmission in Slot <i>s</i>   | 50 |

| 6.1 | Top-level Datapaths of $ECU_i$                    | 6  |

| 6.2 | · · ·                                             | 58 |

|     | 5 5                                               | 59 |

|     |                                                   | 60 |

|     |                                                   | 51 |

| 6.6 |                                                   | 64 |

| 6.7 | 1                                                 | 64 |

| 6.8 |                                                   | 55 |

| 6.9 |                                                   | 66 |

|     | -                                                 | 66 |

|     |                                                   | 57 |

|     |                                                   | 58 |

|     |                                                   | 0  |

|     |                                                   |    |

| CHAPTE | R |

|--------|---|

| ON     | E |

## INTRODUCTION

## 1.1 Motivation

Usually, the motivation section of work in the area of verification talks about exploding rockets, expensive bugs in processors, complex technologies and many other things, which have mostly implicit impact on our everyday life. We would like to talk about technologies, which we deal almost every single day with – and not *implicitly* but *explicitly*: the modern automobiles.

According to the Institute of the Motor Industry:

Electronics account for around 20% of the value of today's average light vehicle, with one supplier, Siemens, stating that 90% of innovations in a modern car can be attributed to electronics development. But here's the rub: DaimlerChrysler blames electronic faults for 70% of its well-publicised quality problems at Mercedes-Benz.<sup>1</sup>

While quality problems do not affect safety, the real problems may arise when the automobile electronics begin to assist the driver in safety-critical functions.

In 2009, Volvo introduced a crossover XC60 with the industry's first auto-breaking feature which serves as an automatic collision detector. The system scans the environment of the moving car using built-in laser sensors to detect a potential collision with a pedestrian or another car, and – in case of a detected obstacle – if the system does not register any driver's reaction to avoid the collision, the car will jab the breaks and stop. While some luxury sedans like the BMW 7 Series and Mercedes Benz S-Class have used similar collision detection systems, their functionality was limited to warnings of the driver only. In Volvo's XC60, the system actively interferes with the car control in case of an emergency.

While such a feature is undoubtedly conductive to safety of the motor traffic, it is important to understand that it is not allowed to produce any false-positive results. If a car full of passengers would be automatically stopped by its error-prone electronics on a highway with high density traffic, such a feature may call for more lives than it will possibly save. The same problems concern any sensor-based safety-critical features, like airbags or stability control.

<sup>&</sup>lt;sup>1</sup>http://www.motor.org.uk/magazine/articles/cover-feature-bugs-in-the-system-101.html

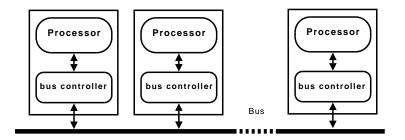

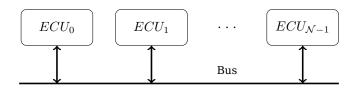

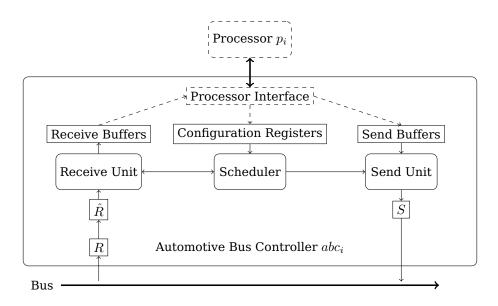

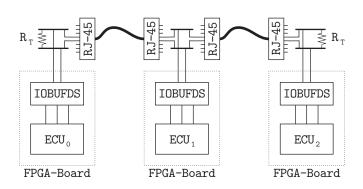

Figure 1.1: Time-Triggered Bus System

Through testing alone, it is infeasible to prove the desired level of reliability [Pik07, BF93]. But on the other hand, verification of an industrial-scale bus system is possibly infeasible in a reasonable amount of time [Pik06]. Previous research contains numerous examples of case studies about verification of isolated parts, protocols and algorithms of time-triggered systems. However, the question whether all these verification efforts carried out with different tools and on different abstraction levels can be combined into one single correctness statement remained open so far.

## 1.2 The Problem

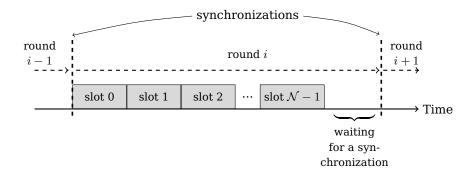

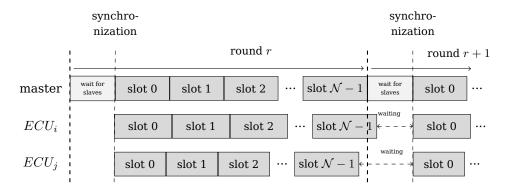

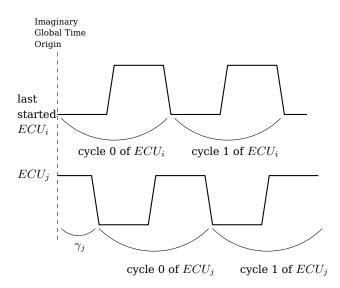

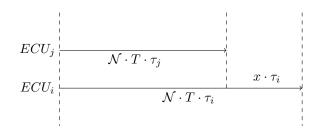

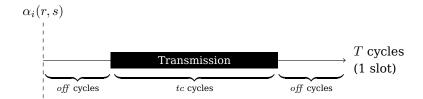

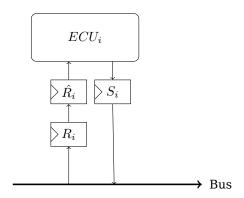

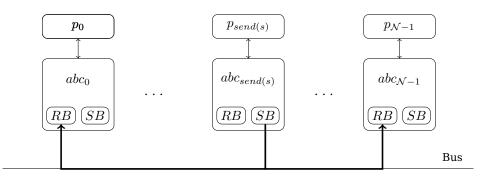

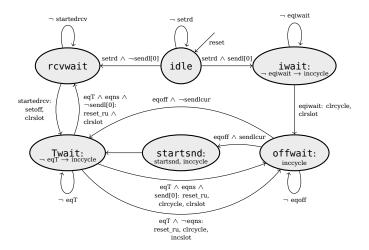

A round-based time-triggered system consists of several units interconnected by a bus as depicted in Figure 1.1. These units function in the following manner. The global time line of the system is split into equal time segments called *rounds*, consisting of several slots. In each slot exactly one unit broadcasts one message over the bus. All other units are listening to the bus in that slot.

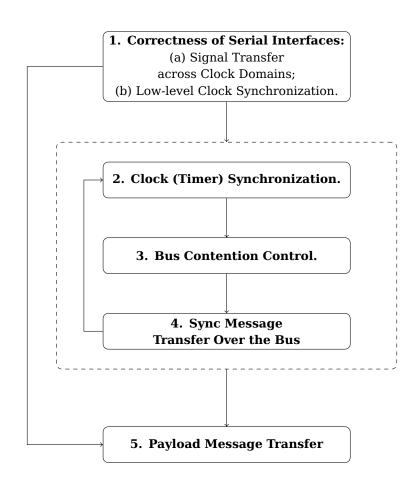

Every unit is clocked by its own oscillator, i.e., units don't share one common discrete time notion. The correctness of message transmission in a time-triggered system can roughly be split into 5 sub-problems as depicted in Figure 1.2. Note that arrows in that figure denote dependencies of sub-problems. Hence, there are five problems to overcome.

- 1. **Correctness of Serial Interfaces.** In order to establish a message transfer over the bus from one unit to another, we need a formalism for an asynchronous signal exchange between two directly connected units: a sender and a receiver. Additionally, the transfer of complex messages requires a low-level protocol synchronization due to clock drift of the sender and the receiver.

- 2. **Clock (Timer) Synchronization.** As in the first problem, the speed differences of units make a synchronization of the common time notion among all participants of the communication necessary. Any software clock synchronization algorithm relies on the message exchange. In the presented time-triggered system, this is rather a simple mechanism and will be realized with the help of *sync messages* (prefixes of ordinary messages indicating the start of a new round). However, the sync messages will be transferred over the bus, which has to be collision-free at the time of the transmission.

- 3. **Bus Contention Control.** The synchronized time notion of all units provides a coordinated behaviour among them, s.t. at each time at most one unit acts as a

Figure 1.2: Decomposition of the Message Exchange Correctness

sender. Hence, it can be shown that no bus contention (a conflict between two senders) can appear during the system run.

- 4. Sync Message Transfer Over the Bus. Since the bus can be proven to be collision-free during all transmission times, we can show, that the sync messages can be transmitted correctly.

- 5. **Payload Message Transfer.** The bus contention control provides a transmission window where the bus can be abstracted to a direct connection between the sender and all receivers; thus, applying the correctness of serial interfaces, the correctness of the payload message transfer can be shown.

Note that Problems 2, 3 and 4 have a cyclic dependency. That means, clock synchronization hinges on message transfer (at least for the synchronization messages), message transfer on bus contention control and bus contention control on clock synchronization. Any theorem stating in isolated form the correctness of clock synchronization, bus contention control or message transfer alone must use hypotheses which break this cycle in one way or the other. If the theorem is to be used as part of an overall correctness proof, then one must be able to discharge these hypotheses in the induction step of a proof arguing simultaneously about clock synchronization, bus contention and message transfer. A paper and pencil proof of this nature can be found in [KP07].

Besides the enumerated problems, another important point is fault-tolerance. Timetriggered systems are usually required to operate in an environment with possibly faulty components and flipped bits during transmission. These faults can be caused by the physical environment or by the error-prone software or hardware. Hence, almost every of the presented problems should tolerate a number of faults bounded by the *fault hypothesis* (assumptions about the frequency, type, location of faults, etc.). We do not deal with fault-tolerance in this thesis, however, we recognize that this problem has to be tackled as soon as the message exchange can be proven in an error-free environment.

Despite the fact that probably every of these five problems were solved by previous research in isolation, to the best of our knowledge, there is not a single previous successful combination of the presented challenges into one uniform correctness statement.

We review the related work in the next section in context of the presented problem decomposition and describe our contribution afterwards.

## **1.3 Related Work**

Verification of real-time systems is by no means new. First efforts were done in the late 80's, tackling the clock synchronization algorithms for fault tolerant systems [RvH89, RvH93, SS92, PSHI99]. These results deal with algorithmical correctness of the clock synchronization only and cover the Problem 2 from Section 1.2. Furthermore, over the last years, several architectures suitable for safety-critical real-time systems were developed. Rushby [Rus01a] gives an overview and a comparison of four of them: SAFEbus, SPIDER, FlexRay and TTA. He also describes [Rus99] a general approach for deriving time-triggered implementations from algorithms specified as functional programs under the assumption of correct message exchange across clock domains (Problem 3, 4) and clock synchronization (Problem 2). He specifies timing constraints,

which a schedule of a time-triggered protocol has to fulfill, to form in its system run so-called *cuts*. These cuts are time segments, where the state of the time-triggered system can be related to a state of its synchronous counterpart. The overall correctness of these implementations would then follow from the correctness of concrete functional programs (which is supposed to be relatively easy), and from the correct transformation of synchronous systems into timed asynchronous implementations.

In [Pik06], Pike has presented several results. One part of his work related to this paper was a corrected and significantly extended version of Rushby's formalism [Rus99]. He also applies this approach to verify the schedule timings of two protocols of the SPIDER bus architecture: Clock Synchronization and Distributed Diagnosis.<sup>2</sup> However, it remains unclear how exactly the timing properties of hardware implementations of these protocols were derived and mapped to the formal model. Moreover, the proposed technique assumes even in the proof of timing properties of a Clock Synchronization protocol already synchronized clocks initially. That is, to extend the proof to correctness for all rounds one needs to use the proposed proof as an induction step. However, to show the initial clock synchronization the correctness of the initialization might become necessary.

Other previous verification efforts – to the best of our knowledge – tackle isolated parts or particular algorithms and protocols of different time-triggered real-time systems. For example, Rushby gives an overview [Rus02] of verified algorithms of TTA. The described verification efforts concern some isolated parts, properties or algorithms of TTA such as clock synchronization, transmission window timing, group membership, etc. Rushby says in this overview: "Some of these algorithms pose formidable challenges to current techniques and have been formally verified only in simplified form or under restricted fault assumptions." For example, the window transmission timing (Problem 3) was verified by Rushby himself [Rus01b] for a transmitter, its bus guardian and a receiver. As in [Rus99] this work assumes the correctness of clock synchronization and correct scheduling mechanism (Problem 1, 2 and 4).

Steiner et al. [SRSP04] verify a startup algorithm for TTA against all possible fail scenarios using a model checker (this might serve as solving of Problem 2 for the initial round). Pike and Brown present in [BP06] a largely automated verification of the Biphase Mark and 8N1 protocols, which covers the Problem 1. They derive a generic model for two asynchronously communicating units, which includes modeling of clock jitter. Their clock model is based on so-called *timeout automata*. The progress of global time is enforced cooperatively by sender and receiver clocks. This model deals with clock jitter but does not model the set up and hold times explicitly. The clock modeling is partially protocol-dependent. Since the sender's clock progress depends on the receiver's clock progress, it is not fully clear how to extend this model to several receiver clocks. Unfortunately, no discussion was provided about the gap between the given stack of abstractions and modeling of actual hardware. Pike and Johnson report in [PJ05] a verification of the Reintegration Protocol of the SPIDER architecture, where this approach was developed.

In [BP07], Brown and Pike show an approach, derived from the classic Abadi-Lamport refinement method, how to use a model checker and an SMT solver to prove temporal refinement of the 8N1 protocol (Problem 1).

In [Pfe03], Pfeifer formally verifies two fault-tolerant algorithms implemented in the Time-Triggered Protocol TTP/C: Group Membership and Clock Synchronization (Prob-

<sup>&</sup>lt;sup>2</sup>Note that no correctness of the synchronous version of these protocols was provided.

lem 2). Both algorithms were analyzed, using a hand-derived mathematical specification of the TTP/C protocol. Group Membership is an algorithm executed on every processor of the bus architecture, which is used to analyze and determine faulty processors to exclude them from the communication. Pfeifer proves the correctness of Group Membership for an untimed system, where all processors work in lock-step sharing one common discrete time notion. Hence, his proof assumes the correctness of underlying asynchronous hardware (Problems 1-5) and could be implemented on the bus interface presented in this thesis.

His Clock Synchronization algorithm uses the arrival times of ordinary messages. However, only the messages comming from processors with accurate clocks will be considered. By his fault hypothesis, in every round, at least the minimal amount of required messages will be transmitted. He does not deal with bus control and message transmission assuming a working message exchange mechanism. Hence, his proof is based on the solved Problem 1 and on an abstraction of the bus to an one to one connection between all processors, or on the solved Problem 4 for a bus architecture.

Both algorithms are mutually dependend for the following reasons.

- Since the messages whose arrival times are used for computation of the clock adjustment should come from non-faulty processors, the correctness of the Group Membership algorithm has to be assumed.

- 2. However, the Group Membership algorithm was proven as an untimed algorithm, which is only possible if Clock Synchronization can be proven to be correct, such that an untimed algorithm can be refined to a timed one.

Although the algorithms are mutually dependend, Pfeifer has analyzed them in isolated form and on different levels of abstraction: the Group Membership was analyzed as an untimed (synchronous) mechanism, whereas the Clock Synchronization was verified in a timed model. He also introduces an abstract induction-based principle how to combine both proofs resolving their mutual dependency.

If we want to integrate both algorithms into the time-triggered system presented in this thesis, we need to extend the circular dependency by a new **Problem 6:** the Group Membership. This 6th problem would depend on Problems 1-5, and the Problem 2 becomes dependend on Problem 6.

Some interesting results were recently achieved with the Uppaal model checker. Gerke et al. [GEFP10] presented a fully automatic proof of the message transmission on the physical layer protocol of FlexRay describing the underlying model as a network of *timed automata*. They model the asynchronously communicating part of the FlexRay hardware as proposed in [Sch07], which was developed in Verisoft project for the automotive system presented in this thesis. The proof was carried out under the assumption of working TDMA schedule (this implies clock synchronization), which is maintained by high-level protocols. Hence, they have solved Problem 1 fully automatically.

Furthermore, assuming clock synchronization Zhang [Zha06] has proven two properties of the scheduling protocol of a FlexRay bus guardian: the correct relay and message integrity.

Almost all of these efforts deal with conceptual correctness of algorithms without linking them to concrete asynchronously communicating hardware models. Moreover, it would be highly desirable to reuse some of the developed techniques or proven algorithms and to consolidate them into one single theory. However, it is not clear, how to combine these results taking into account the fact, that these theories were made

Figure 1.3: Direct Connection of Serial Interfaces

using different formalisms, different verification environments and are formulated at different levels of abstractions.

## **1.4 Contribution to the "Automotive" Project**

The work presented in this thesis was started as subproject "Automotive" of the Verisoft project. Verisoft is a long-term research project funded by the German Federal Ministry of Education and Research. One of the goals of Verisoft is the formal pervasive verification of computer systems including all levels from gate-level hardware to user applications.

In contrast to related work, Verisoft has tackled the problem of pervasive verification of a distributed time-triggered system from another side. Instead of verifying an industrial-scale bus system, a simple but flexible and extendible architecture influenced by the FlexRay standard [Con06] with simple synchronization and communication protocols was developed at the gate and register level. The system consists of bus interfaces implemented on gate and register level, interconnected by a bus. The modeling of the asynchronous communication relies on a precise timing model of hardware registers obtained by formalization of data sheets for hardware components.

The theoretical foundations of this work were formulated in computer science lectures "Computer Architecture 2" [Pau05] by Wolfgang Paul and published in [KP07]. Previous verification efforts were reported in [Sch07] and [Böh07].

In [Sch07], Schmaltz has proven the correctness of serial interfaces (Problem 1) of the presented bus controller and the payload message transfer (Problem 5) under the assumption of two directly connected and appropriatelly initialized units. That means, Schmaltz's results can be used as soon as Problems 2, 3 and 4 are solved.

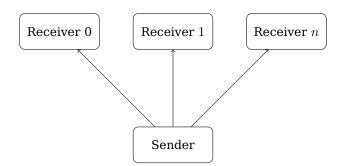

In [Böh07], Böhm has used the correctness of serial interfaces provided by Schmaltz and has shown the transmission of sync messages (Problem 4) and resulting Clock Synchronization (Problem 2) for one sender and arbitrary receiver under the assumption that every receiver is directly connected to the sender as depicted in Figure 1.3. Thus, he could ignore the Problem 3, because no notion of the bus was introduced.

Hence, to couple these two results into one theory, filling of the last gap, namely, solving of the Problem 3 was necessary. The extension and consolidation of previous results into a single correctness theorem presented in this thesis was reported in [PM11], hence, some passages of this publication coincide with this thesis literally.

In this case study, we have verified the message transmission over the bus relying on the minimal set of hypotheses like bounded clock drift. The design of the bus controller can be automatically translated into Verilog and deployed on FPGAs. Our contribution is the first complete formal verification of a FlexRay-like bus interface at the gate and register level.

## 1.5 Tools

The gate-level implementation of the bus controller which will be presented in this thesis was carried out [Kna08] in the specification language of the interactive theorem prover Isabelle/HOL [NPW02]. The Isabelle/HOL specification language is an extension of functional programming language ML.

The verification of the controller was carried out in Isabelle/HOL supported by the symbolic model checker NuSMV [CCG<sup>+</sup>02], which was integrated [Tve05] into Isabelle/HOL. NuSMV is an open source re-implementation of the model checker CMU SMV [CCG<sup>+</sup>98] for CTL and LTL properties. We have used NuSMV to verify temporal properties of the system defined over Kripke structures [Gup93] and as an external BDD decision procedure. To verify a property by NuSMV, we have formulated this property as an LTL formula and applied IHaVeIt [Tve05] to it.

IHaVeIt is a translation tool, which translates Isabelle's specification language into NuSMV input language. Moreover, it consists of several algorithms for handling uninterpreted functions and data abstractions used in Isabelle models.

After the Isabelle code is translated from Isabelle to NuSMV language, the NuSMV model checker can be applied to it. We will present all lemmas in higher-order logic notation.

Another benefit of the IHaVeIt tool is the possibility to translate a gate-level hardware implemented in Isabelle/HOL specification language directly to Verilog fully automatically. This was used [End09] to translate the bus controller implementation into Verilog and to deploy it on three interconnected FPGAs.

## **1.6 Outline**

In Chapter 2 we introduce the notation and concepts we use during modeling and verification; we introduce boolean gates and circuits representing basic blocks in the hardware design of the studied bus controller.

In Chapter 3 we formalize the communication scheme used in our FlexRay-like timetriggered system. The communication scheme is based on the Time Division Multiple Access strategy and hinges on recurrent clock synchronization of all units participating in the communication.

In Chapter 4 we describe how a clock domain crossing communication is modeled [Sch07] by developing a register model with precise timing and linking it to a digital hardware model. Furthermore, we extend this model to a communication bus interconnecting all units of the time-triggered system. We also present and extend the results of previous efforts in the verification of the low-level signal transition among different clock domains.

In Chapter 5 we formulate the correctness criteria for message transmission in our time-triggered system and decompose it into three milestones.

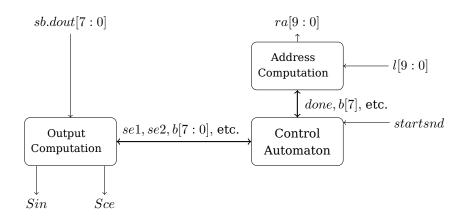

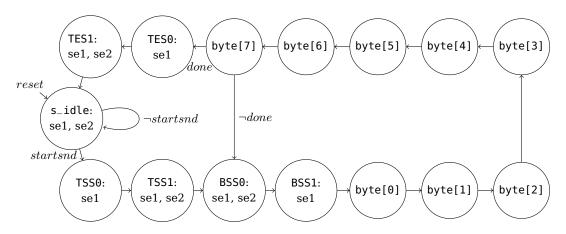

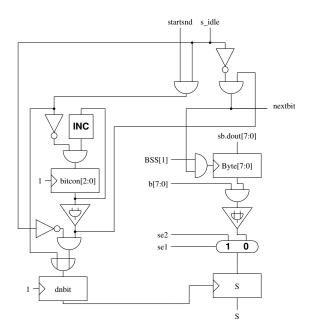

In Chapter 6 we show the implementation of relevant parts of the bus controller and introduce the used message protocol.

In Chapter 7 we present previous verification [Böh07] of the schedule timing and clock synchronization within a single round under the assumption of a direct connection between the sender and all receivers. We use these results and present the verification of bus contention control property, allowing us to abstract the bus connection between the sender and every receiver as a direct wire. This allows us to apply results from Chapter 4 to show the correctness of high-level message transmission [Sch07].

Finally, in Chapter 8 we use the theorem about the contention control and apply the hardware correctness of serial interfaces to show the high-level transmission correctness.

In Chapter 9 we conclude our work, discuss future work and give some statistics.

## CHAPTER **TWO**

## BASICS

## 2.1 Notation

In this thesis we use following notation.

#### Operators

- the operator := denotes an assignment, e.g., in a := b we assign value b to identifier a

- the operator  $\equiv$  denotes equivalence of expressions

#### Sets

- $\mathbb{B} := \{0, 1\}$

- +  $\mathbb{B}^*$  is a set of all tupels with elements from  $\mathbb B$

- ${\mathbb R}$  is the set of real numbers

- +  $\ensuremath{\mathbb{Z}}$  is the set of integers

- +  ${\mathbb N}$  is the set of natural numbers without  ${\bf 0}$

- $\mathbb{N}_0 := \mathbb{N} \cup \{0\}$

Intervals For  $a, b, c \in \mathbb{R}$  we define:

- $[a:b] := \{x \mid a \le x \le b\}$

- $[a:b) := \{x \mid a \le x < b\}$

- $(a:b] := \{x \mid a < x \le b\}$

- $(a:b) := \{x \mid a < x < b\}$

#### **Bits and Bitvectors**

- if  $b \in \mathbb{B}$  then we call b a *bit*

- if a and b are bits then we denote by  $a \circ b$  a concatenation of bits a and b

- a concatenation of bits is also called a bitvector

- if a and b are bitvectors then we denote by  $a \circ b$  a concatenation of bitvectors a and b, which is a bitvector again

- if b is a bitvector, then b[i] is its i'th bit, counting right to left (little endian)

- if *b* is a bitvector of length *n*, then we also refer to it by b[n 1:0]

- a bitvector of length 1 is a bit

- if  $a \in \mathbb{B}, n \in \mathbb{N}$  then we denote by  $a^n$  a bitvector  $\underline{a \circ a} \circ \underline{\dots \circ a}$

$$n$$

times

#### Functions

• Let *b* be a bitvector of length *n*, then we encode *b* as a natural number by function  $\langle \cdot \rangle$  as follows:

$$\langle b \rangle := \sum_{i=0}^{n-1} b[i] \cdot 2^i$$

- if  $i < 2^n$  for  $n \in \mathbb{N}$  then  $bin_n(i)$  returns the bitvector of length n, which represents number i (note:  $i = \langle bin_n(i) \rangle$ )

- For  $x \in \mathbb{R}$  we define the flooring and ceiling operators:

- $\lfloor x \rfloor = max \{ a \in \mathbb{Z} \mid a \le x \}$

- $[x] = \min\{a \in \mathbb{Z} \mid x \le a\}$

## 2.2 Trace Semantics

Note that our hardware model of the entire time-triggered system goes beyound the ordinary digital hardware model. Since we want to argue about a set of asynchronously working units within different clock domains, we need to extend the usual hardware model by more precise timing parameters such as setup and hold times. We also must deal with undefined and metastable signals. We will introduce this extension in Chapter 4.

The hardware presented within a clock domain consists of finite data structures only and has a deterministic behaviour. To model hardware we split it into hardware states (configurations) and a transition function over them. The state of a hardware can be characterized by the contents of its registers and memories. These registers change their content from cycle to cycle according to the logical circuits, placed at their inputs. We can represent a digital hardware model and its computations as a finite Mealy automaton [MP00]:

$(S, S_0, \Sigma, \Lambda, \delta, \eta)$

It consists of the following:

- a finite set of hardware states *S*;

- a set of initial states  $S_0 \subset S$ ;

- a finite set of all possible register inputs  $\Sigma$ ;

- a finite set of all possible register outputs  $\Lambda$ ;

- a transition function  $\delta: S \times \Sigma \to S$ ;

- an output function  $\eta: S \times \Sigma \to \Lambda$ .

The transition function takes a hardware state, register inputs and produces a new configuration of the bus controller. The output function takes a hardware state, register inputs and outputs register contents of the next hardware state.

Moreover, we fix an abstract trace function  $trace : \mathbb{N} \to S$ , which assigns a hardware state to each natural number. We also fix a similar function for register inputs:  $inputs : \mathbb{N} \to \Sigma$ .

We call the function trace a valid execution trace if it produces an initial configuration for cycle 0 and each consecutive configuration is computed by applying the transition function once:

$$trace(0) \in S_0 \land \forall i : trace(i+1) = \delta(trace(i), inputs(i))$$

Such a valid execution trace represents a computation of the real hardware. Each hardware state of the model is represented in a real hardware by contents of its registers and RAMs. The transition function is then realized by logical gates and combinational circuits.

In this thesis we will refer to a hardware state of some model h in cycle i by  $h^i$ , which denotes the configuration returned by the trace function for number i:

$$h^i := trace(i)$$

We will always assume that used trace functions are valid execution traces.

Moreover, we denote by  $h^i R$  the content of register R of hardware state h in cycle i, and by  $f(h^i)$  a boolean signal derived from other register contents and boolean gates of hardware state h in cycle i. Sometimes, we will abbreviate  $h^i R$  by  $R^i$  and  $f(h^i)$  by  $f^i$ . The same notation and abbreviatation is also used for a memory content  $h^i M$ .

## 2.3 Boolean Gates and Basic Circuits

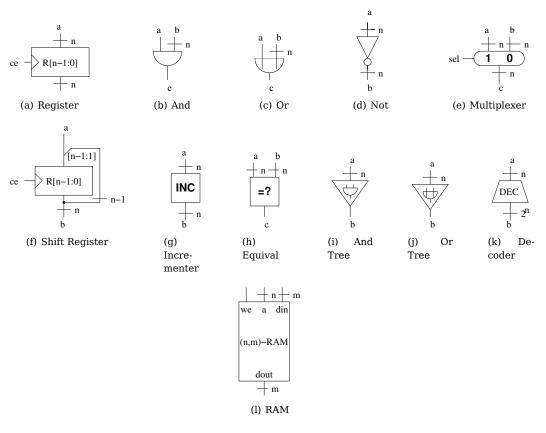

In the description of the hardware design we use the following boolean gates and curcuits.

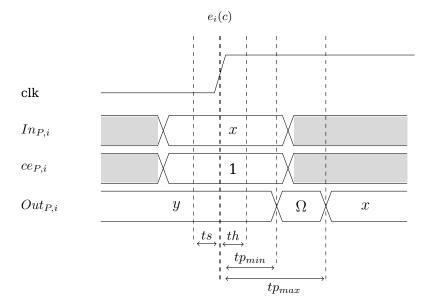

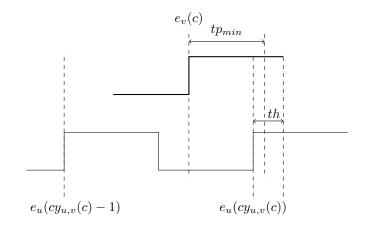

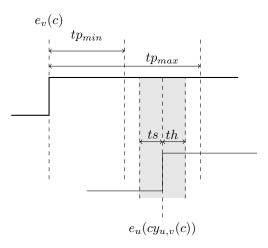

• **Register** is depicted in Figure 2.1(a); it stores a bitvector of length n (or one bit, in case n = 1) and has the following semantics. Let  $R^i$  be the content of register R in cycle i and let  $a^i$  be the input and  $ce^i$  be the clock enable signal of register R in cycle i.

$$R^{i+1} = \begin{cases} a^i & : ce^i = 1\\ R^i & : \text{otherwise} \end{cases}$$

Figure 2.1: Boolean Gates and Circuits

• AND Gate depicted in Figure 2.1(b) has the following semantics. Let  $a \in \mathbb{B}$  and  $b \in \mathbb{B}^n$  with  $n \in \mathbb{N}$ . Then its output  $c \in \mathbb{B}^n$  is specified as:

$$\forall i \in [0:n-1]: c[i] := a \land b[i]$$

Hence, it computes logical conjunction of a bit and a bitvector.

- **OR** Gate depicted in Figure 2.1(c) computes disjunction of a bit and a bitvector and is specified analogously to the AND Gate in a straightforward way.

- **NOT** Gate depicted in Figure 2.1(d) flips every bit of the input bitvector  $a \in \mathbb{B}^n$  with  $n \in \mathbb{N}$ . Its output  $b \in \mathbb{B}^n$  is specified as:

$$\forall i \in [0:n-1]: b[i] := \neg a[i]$$

• **Multiplexer** Gate depicted in Figure 2.1(e), its output  $c \in \mathbb{B}$  is specified as:

$\forall n \in \mathbb{N}, a, b \in \mathbb{B}^n, sel \in \mathbb{B} : c :=$ if sel then a else b

• Shift Register depicted in Figure 2.1(f) is a tuple of 1-bit registers

$(R_{n-1}, ..., R_0)$

with  $n \in \mathbb{N}$ , which are always clocked. The registers are connected, s.t. for all cycles  $c \in \mathbb{N}$  and input  $a \in \mathbb{B}$  holds:

$$R_{n-1}^{c} = a^{c-1} \land \forall i \in [0:n-2] : R_{i}^{c+1} = R_{i+1}^{c}$$

Its output  $c \in \mathbb{B}^n$  is specified as follows:

$$\forall i \in [0:n-1]: c[i] = R_i$$

- **Incrementer** circuit is depicted in Figure 2.1(g), it increments a bitvector b of length n by one. The overflow bit will be skiped, thus, incrementing of bitvector  $1^n$  yields  $0^n$ .

- **Equivalence** circuit depicted in Figure 2.1(h) compares two bitvectors. Its output  $c \in \mathbb{B}$  is computed as:

$$\forall n \in \mathbb{N}, a, b \in \mathbb{B}^n : c := (a = b)$$

And Tree circuit depicted in Figure 2.1(i) computes the conjunction of all bits of the input bitvector a ∈ B<sup>n</sup> with n ∈ N. The output b ∈ B is specified as:

$$b = \bigwedge_{i \in [0:n-1]} a[i]$$

- **Or Tree** circuit depicted in Figure 2.1(j) is a counterpart of the And Tree for the logical OR operation.

- **Decoder** circuit depicted in Figure 2.1(k) interprets the given bitvector as a number and outputs this number as a unary bitvector (see Terminology below). Let  $a \in \mathbb{B}^n$  with  $n \in \mathbb{N}$ . Then, the output  $b \in \mathbb{B}^{2^n}$  of the Decoder Circuit is specified as:

$$b = 0^{2^n - 1 - \langle a \rangle} 10^{\langle a \rangle}$$

(n,m)-RAM circuit depicted in Figure 2.1(l) is used to store bitvectors of length m. Each bitvector will be addressed by a n-bit address bitvector. A RAM circuit has input ports we, a and din – for write enable signal, address and input data, respectively. It has following semantics. Let M be a (n,m)-RAM. Then:

$$M^{i+1}(addr) = \begin{cases} din^{i} & : we^{i} = 1 \land a^{i} = addr \\ M^{i}(addr) & : \text{ otherwise} \end{cases}$$

## 2.4 Terminology

- We understand under a **clock domain** the scope of a system (a set of registers), where the time can be measured with the help of *one* clock. For example, if two circuits  $c_1$  and  $c_2$  are clocked by two different clocks, then we would refer to all registers of  $c_1$  as being in the clock domain of circuit  $c_1$ ; analogously, all register of  $c_2$  would be in the clock domain of  $c_2$ .

- A value computed by logical gates and circuits within one clock domain is called a **signal**; we say it is **active**, if the computed signal has the value '1'; the signal is **inactive** otherwise.

• Later we will deal with instability and undefined behaviour of analog registors. An undefined register value will be denoted by  $\Omega$ . Moreover, we will call a function s an **analog signal** if it is typed as follows:

$$s: \mathbb{R} \to \{0, 1, \Omega\}$$

The analog signal s is **active** at time t if s(t) = 1; it is **inactive** if s(t) = 0; it is **undefined** if  $s(t) = \Omega$ .

• We say a bitvector is **unary** if it has the form  $0^i \circ 1 \circ 0^j$  for some  $i \in \mathbb{N}$  and  $j \in \mathbb{N}_0$ .

| CHAPTER |  |

|---------|--|

| THREE   |  |

# COMMUNICATION MODEL OF A SIMPLE FLEXRAY-LIKE TIME-TRIGGERED BUS SYSTEM