# Analysis of Preemptively Scheduled Hard Real-time Systems

# Dissertation

zur Erlangung des Grades des Doktors der Ingenieurwissenschaften der Naturwissenschaftlich-Technischen Fakultäten der Universität des Saarlandes

Sebastian Altmeyer

von

Saarbrücken 2012 Dekan: Prof. Dr. Mark Groves

Prüfungsausschuß: Prof. Dr. Sebastian Hack (Vorsitzender)

Prof. Dr. Reinhard Wilhelm (Gutachter) Prof. Dr. Gerhard Fohler (Gutachter) Laurent Mauborgne, PhD (Gutachter)

Dr. Daniel Grund (akademischer Mitarbeiter)

Tag des Kolloqiums: 25. Oktober 2012

Impressum

Copyright: © 2012 Sebastian Altmeyer

Druck und Verlag: epubli GmbH, Berlin, www.epubli.de

ISBN 978-3-8442-5161-6

# ABSTRACT

As timing is a major property of hard real-time, proving timing correctness is of utter importance. A static timing analysis derives upper bounds on the execution time of tasks, a scheduling analysis uses these bounds and checks if each task meets its timing constraints.

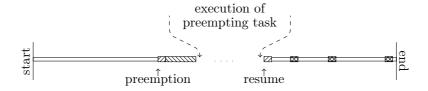

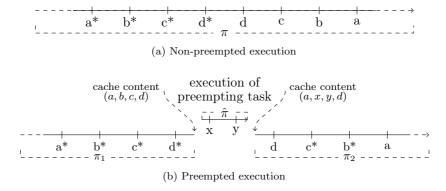

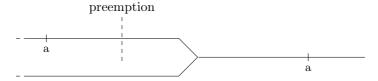

In preemptively scheduled systems with caches, this interface between timing analysis and scheduling analysis must be considered outdated. On a context switch, a preempting task may evict cached data of a preempted task that need to be reloaded again after preemption. The additional execution time due to these reloads, called cache-related preemption delay (CRPD), may substantially prolong a task's execution time and strongly influence the system's performance.

In this thesis, we present a formal definition of the cache-related preemption delay and determine the applicability and the limitations of a separate CRPD computation.

To bound the CRPD based on the analysis of the preempted task, we introduce the concept of definitely cached useful cache blocks. This new concept eliminates substantial pessimism with respect to former analyses by considering the over-approximation of a preceding timing analysis.

We consider the impact of the preempting task to further refine the CRPD bounds. To this end, we present the notion of resilience. The resilience of a cache block is a measure for the amount of disturbance of a preempting task a cache block of the preempted task may survive.

Based on these CRPD bounds, we show how to correctly account for the CRPD in the schedulability analysis for fixed-priority preemptive systems and present new CRPD-aware response time analyses: ECB-Union and Multiset approaches.

# ZUSAMMENFASSUNG

Da das Zeitverhalten ein Hauptbestandteil harter Echtzeitsysteme ist, ist das Beweisen der zeitlichen Korrektheit von großer Bedeutung. Eine statische Zeitanalyse berechnet obere Schranken der Ausführungszeiten von Programmen, eine Planbarkeitsanalyse benutzt diese und prüft ob jedes Programm die Zeitanforderungen erfüllt.

In präemptiv geplanten Systemen mit Caches, muss die Nahtstelle zwischen Zeitanalyse und Planbarkeitsanalyse als veraltet angesehen werden. Im Falle eines Kontextwechsels kann das unterbrechende Programm Cachedaten des unterbrochenen Programms entfernen. Diese Daten müssen nach der Unterbrechung erneut geladen werden. Die zusätzliche Ausführungszeit durch das Nachladen der Daten, welche Cache-bezogene Präemptions-Verzögerung (engl. Cache-related Preemption Delay (CR-PD)) genannt wird, kann die Ausführungszeit des Programm wesentlich erhöhen und hat somit einen starken Einfluss auf die Gesamtleistung des Systems.

Wir präsentieren in dieser Arbeit eine formale Definition der Cachebezogene Präemptions-Verzögerung und bestimmen die Einschränkungen und die Anwendbarkeit einer separaten Berechnung der CRPD.

Basierend auf der Analyse des unterbrochenen Programms präsentieren wir das Konzept der definitiv gecachten nützlichen Cacheblöcke. Verglichen mit bisherigen CRPD-Analysen eleminiert dieses neue Konzept wesentliche Überschätzung indem die Überschätzung der vorherigen Zeitanalyse mit in Betracht gezogen wird.

Wir analysieren den Einfluss des unterbrechenden Programms um die CRPD-Schranken weiter zu verbessern. Hierzu führen wir das Konzept der Belastbarkeit ein. Die Belastbarkeit eines Cacheblocks ist ein Maß für die Störung durch das unterbrechende Programm, die ein nützlicher Cacheblock überleben kann.

Basierend auf diesen CRPD-Schranken zeigen wir, wie die Cachebezogene Präemptions-Verzögerung korrekt in die Planbarkeitsanalyse

für Systeme mit statischen Prioritäten integriert werden kann und präsentieren neue CRPD-bewußte Antwortzeitanalysen: die ECB-Union und die Multimengen-Ansätze.

# ACKNOWLEDGEMENTS

This thesis would not have been possible without the help and support of many people. Foremost, I like to thank Prof. Reinhard Wilhelm for his advise and guidance and for giving me the opportunity to write this PhD thesis. I have spent wonderful years at his chair at Saarland University and learned a lot during this time. I also owe thanks to Prof. Gerhard Fohler and Laurent Mauborgne for carefully reviewing my thesis and to Prof. Sebastian Hack and Dr. Daniel Grund as members of the examination board.

Substantial parts of this thesis originated from collaboration with other researchers: I like to express my gratitude to Claire Maiza, Jan Reineke and Robert Davis. It was a real pleasure to work with such bright and motivated colleagues and friends.

I thank Sascha El-Abed, Michael Gerke, Jörg Herter and Verena Kremer for carefully proofreading drafts of my thesis. I also like to thank my friends, and family for their support. I always had sufficient distraction to regain energy for the often tedious work. Last but not least, I thank Kim for her love and encouragement, especially during the last few months of my PhD studies.

# CONTENTS

| 1. | Intro | oduction 1                                   |

|----|-------|----------------------------------------------|

|    | 1.1.  | Contributions of this Thesis                 |

|    | 1.2.  | Structure                                    |

| 2. | Abst  | tract Interpretation                         |

|    | 2.1.  | Program Analysis                             |

|    |       | 2.1.1. Collecting Semantics                  |

|    | 2.2.  | Abstract Interpretation                      |

|    | 2.3.  | Fixed-Point Analysis                         |

| 3. | Bac   | kground 19                                   |

|    | 3.1.  | Real-Time Scheduling                         |

|    |       | 3.1.1. Sporadic Task Model                   |

|    |       | 3.1.2. Priority-Driven Scheduling            |

|    |       | 3.1.3. Mutual Exclusion                      |

|    | 3.2.  |                                              |

|    |       | 3.2.1. Principle of Locality                 |

|    |       | 3.2.2. Processor Caches                      |

|    |       | 3.2.3. Replacement Policy                    |

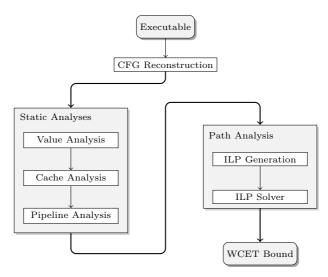

|    | 3.3.  | Timing and Cache Analysis                    |

|    |       | 3.3.1. Components of a Timing Analysis       |

|    |       | 3.3.2. Cache Analysis                        |

| 4. | Con   | text-Switch Costs 49                         |

|    | 4.1.  | The Impact of a Context Switch               |

|    | 4.2.  | Cache-related Preemption Delay               |

|    |       | 4.2.1. Early Work on CRPD                    |

|    |       | 4.2.2. Formal Definitions                    |

|    | 4.3.  | Limitations of the CRPD Approach 54          |

|    |       | 4.3.1. Classification of Architectures 54    |

|    |       | 4.3.2 CRPD and Cache Replacement Policies 55 |

|    | 4.4. (  | Other Approaches to the Analysis of Preemptive Systems                                        | 58        |

|----|---------|-----------------------------------------------------------------------------------------------|-----------|

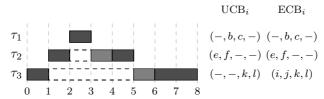

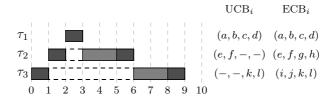

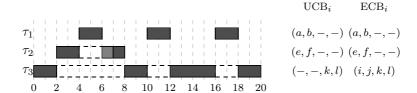

| 5. |         | ding Cache-Related Preemption delay—Related Work Useful Cache Blocks; Lee's Original Approach | <b>61</b> |

|    | 5.1. t  | Evicting Cache Blocks                                                                         | 63        |

|    |         | Combining ECBs and UCBs                                                                       | 64        |

|    |         | Deriving the Set of UCBs/ECBs                                                                 | 65        |

| 6. | Defini  | itely-Cached Useful Cache Blocks                                                              | 67        |

|    | 6.1. I  | Pessimism in Lee's Approach                                                                   | 68        |

|    | 6.2. I  | Definitely-Cached UCBs                                                                        | 69        |

|    | 6       | 3.2.1. Correctness                                                                            | 71        |

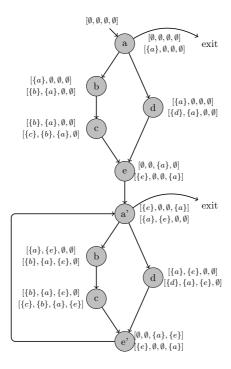

|    | 6.3. I  | Deriving the Set of DC-UCBs                                                                   | 73        |

| 7. |         | ) for LRU Caches—Resilience Analysis                                                          | 79        |

|    |         | CRPD for LRU Caches                                                                           | 80        |

|    | 7.2. I  | Resilience of a Cache Block                                                                   | 81        |

|    |         | 7.2.1. Multiple Preemptions                                                                   | 84        |

|    |         | 7.2.2. Correctness                                                                            | 85        |

|    | 7.3. I  | Resilience Analysis                                                                           | 87        |

| 8. |         | nption cost aware Response Time Analysis                                                      | 95        |

|    | 8.1. I  | Existing Approaches                                                                           | 96        |

|    | 8       | 8.1.1. ECB-Only & UCB-Only                                                                    | 97        |

|    |         | 8.1.2. UCB Union                                                                              | 99        |

|    |         | 8.1.3. Multiset Approaches                                                                    |           |

|    |         | ECB Union                                                                                     |           |

|    |         | Multiset Approaches                                                                           |           |

|    | 8.4. I  | Resource Access Protocols and Preemption Cost                                                 | 108       |

| 9. | Evalu   |                                                                                               | 111       |

|    |         | Target Architecture                                                                           |           |

|    |         | Benchmarks                                                                                    |           |

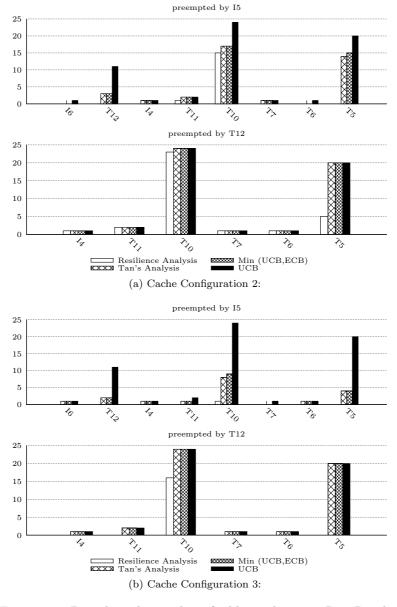

|    |         | DC-UCB Analysis                                                                               |           |

|    |         | Resilience Analysis                                                                           |           |

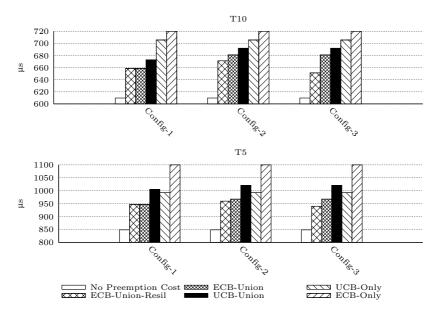

|    |         | CRPD Aware Scheduling Analysis                                                                |           |

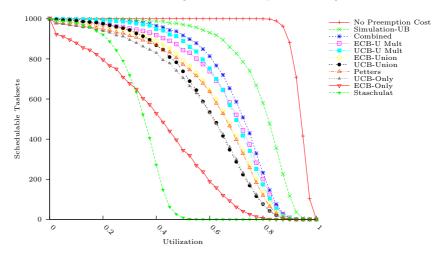

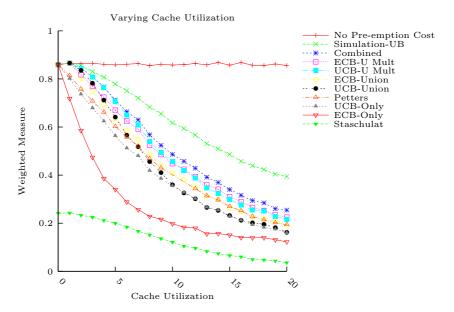

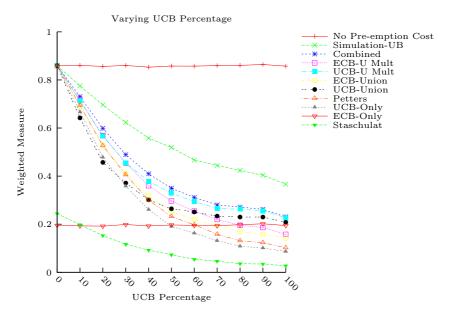

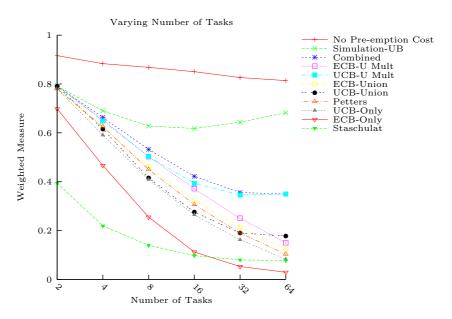

|    | E       | 9.5.1. Randomly Generated Task Sets                                                           | 119       |

| 10 |         | usions                                                                                        | 127       |

|    |         | Summary of Contributions                                                                      |           |

|    |         | Future Work                                                                                   |           |

|    | 10.3. ( | Conclusions                                                                                   | 129       |

|                 | Contents |

|-----------------|----------|

| Bibliography    | 131      |

| Index           | 143      |

| List of Figures | 145      |

| List of Tables  | 147      |

| A. UCB Analysis | 149      |

| B. Proofs       | 155      |

# INTRODUCTION

Safety doesn't happen by accident. *Unknown*

In our everyday life, we are surrounded by small computer systems, embedded into larger devices such as cars, trains, airplanes, but also mobile phones, washing machines and refrigerators. Most of these *embedded* computers are *real-time systems*, i.e., they are subject to real-time constraints. Correctness of such systems does not only depend on the correct result of the computation, but also on the timeliness of the result. An airbag controller, for instance, has not only to decide whether or not to inflate the airbag, but has to do so before the driver's head bangs on the steering wheel. A drive-by-wire system is not allowed to introduce long delays, but must translate the driver's steering motion and pass it to the wheels in time. A flight control system must quickly compensate external disturbances to prevent stalls and thus to keep the airplane in stable flight. Railroad signalling, pacemakers, monitoring in a nuclear power plant... This list can be extended to plenty of other areas and examples.

Real-time systems are divided into *soft* and *hard real-time systems* depending on whether a single deadline miss is tolerable (*soft*) or is considered a complete failure (*hard*). As timing behavior is a major property of such systems, proving timing correctness is of utter importance during the development process. Functionality of an embedded system

is typically implemented by a set of tasks distributed to the available hardware and processing units. Proving timing correctness of the complete systems is thus traditionally a two-step approach:

- 1. deriving bounds on the execution times of tasks in isolation, and

- 2. distributing tasks to the available resources (e.g. processing units) guaranteeing that all tasks comply with their timing constraints.

Common denomination for theses steps are  $timing\ analysis$  and  $scheduling\ analysis$ .

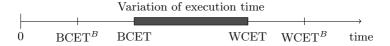

Timing Analysis can either be static or dynamic. Which one to apply depends on the criticality of the system. *Dynamic timing analysis*, also known as measurement-based approach, explores a task's execution time for varying inputs and initial processor states. As exhaustive measurement is usually infeasible, it is unlikely that the actual *best-case* or *worst-case* execution time will be encountered. Hence, dynamic timing analysis does not provide guaranteed bounds on the execution times but only educated guesses. It is thus used for soft real-time systems or systems with less stringent timing constraints.

Static timing analysis employs an abstract model of the hardware to characterize the timing behavior of a task. It derives bounds on the execution time without any concrete execution of a task but based on the abstract model. A static timing analysis is required to be safe, i.e., execution time bounds must be conservative and is demanded to be precise, i.e., execution time bounds should be as close as possible to the actual best-case or worst-case timing behavior. In contrast to measurement-based approaches, static timing analyses can provide guaranteed bounds (assuming a sound abstract hardware model). It is thus more apt for hard real-time systems.

Scheduling Analysis determines if each task complies with its timing constraints when scheduled according to a predefined scheduling policy. Timing constraints are typically defined by a task's period and a task's deadline, both determined by the physical environment. Tasks are scheduled either *preemptively*, i.e., task's execution can be temporarily interrupted, or *non-preemptively*, i.e., once started each task runs to completion. Preemptive schedules are potentially more powerful in the sense that some task sets are only schedulable preemptively. Tasks with short deadlines—such as interrupts—usually can not postpone their execution until the completion of the currently running task.

An important class of schedulers are *priority driven schedulers* where each task is assigned (either statically or dynamically) a priority. The scheduler always executes the task with the highest priority among all currently available tasks.

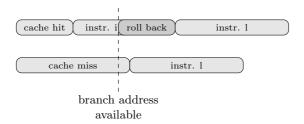

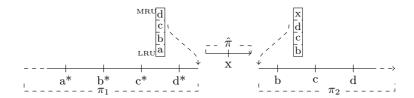

#### Traditional Interface

Traditionally, the complete interface between timing analysis and scheduling analysis is given by bounds on the tasks' execution times. Other input to the scheduling analysis—such as deadlines or periods of tasks—are dictated by the system's environment and bypass the timing analysis. However, this interface is inherently pessimistic and can be considered outdated for modern hardware architectures. Since the advent of caches in embedded real-time systems, history-sensitive architectural components go beyond the scope of a task. This holds especially for preemptively scheduled systems. On a task preemption or *context switch*, the preempting task disrupts the current processor state and may evict useful cached data of the preempted task. After preemption, the execution time of the preempted task strongly depends on whether previously cached data is still resident in cache. The additional execution time due to preemption is denoted *context switch costs* and the portion of the context switch costs caused by additional cache reloads cache-related preemption delay.

Recent studies show a substantial increase of the execution times due to preemption [10, 14, 78]. Ignoring these costs is thus not an option as it leads to optimistic results. Instead, most scheduling analyses assume that the execution time bound already accounts for the additional context switch costs—as proposed in the seminal paper by Liu and Layland [53] that laid the foundation of the scheduling theory. This assumption however is inherently pessimistic for cached systems: A sound upper bound on the execution time must conservatively account for each scheduling scenario and each possible number of preemptions.

# 1.1. Contributions of this Thesis

This thesis advocates a different approach to the analysis of preemptively scheduled hard real-time systems: **Precise modelling and computation of the context switch costs.** Instead of limiting the interface between timing and scheduling analysis to a single scalar value (upper bound on the execution time), we propose to extend timing analysis to

compute precise preemption costs and to integrate these costs into the scheduling analysis.

The first scheduling analysis explicitly considering preemption costs has been proposed by Busquets-Mataix et al. [18] (based on the assumption that each cache entry must be reloaded). This model has been refined by Lee et al. [49] by computing the worst-case impact on the preempted task, by Tomiyama et al. [90], and later Tan et al. [86] by considering preempting and preempted tasks.

We contribute to this line of research in the following ways and aspects:

#### Formal Model of the Cache-Related Preemption Delay

We provide a formal definition of the cache-related preemption delay. Advantages of this model are twofold: First, we are able to base all subsequent analyses on solid ground and prove the correctness of the proposed CRPD analyses. Second, we provide a clear identification of the applicability and the limitations of a separate computation of the context switch costs. We show that in contrast to prior beliefs, context switch costs of a single preemption can be unbounded in case of certain cache replacement policies and hardware features.

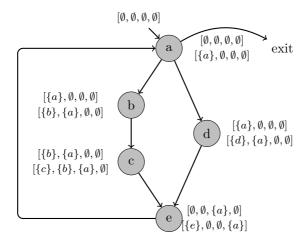

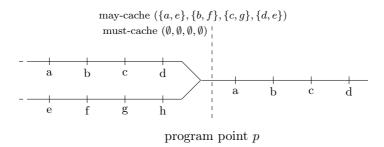

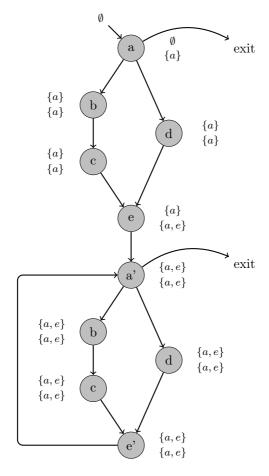

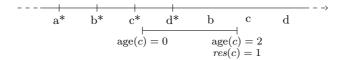

#### Concept of Definitely-Cached Useful Cache Blocks

We identify substantial pessimism in the first analysis of the context switch costs based on the preempted task and propose a new preciser model using the concept of definitely-cached useful cache blocks (DC-UCBs). A useful cache block is a memory that is i) cached prior to a program point and ii) reused afterwards. In case of preemption at this program point, only useful cache blocks have to be reloaded and thus can increase the execution time. We improve on the basic concept by considering possible pessimism of the preceding timing analysis that derives an upper bound on the execution time. Furthermore, we prove the correctness of this new model and propose a static program analysis (based on the framework of abstract interpretation) to derive the set of DC-UCBs.

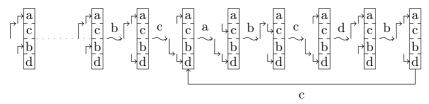

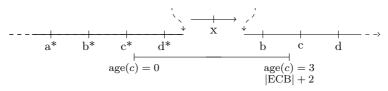

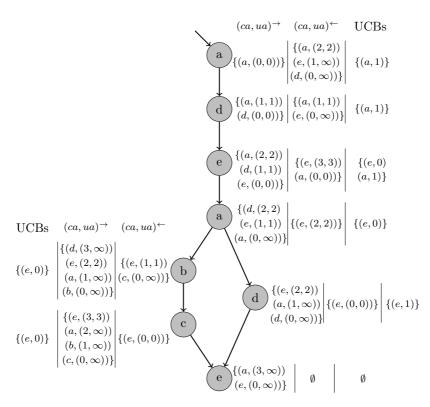

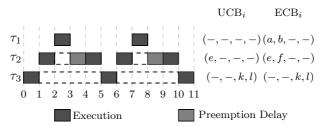

# Resilience Analysis

We improve the bound on the cache-related preemption delay by considering the cache usage of the preempting task. This is especially problematic for set-associative caches. First we show that previous analyses for this setting are unsound and possibly optimistic. We then correct these bounds and present a new, precise, and sound CRPD analysis for set-associative caches. To this end, we introduce the notion of *resilience*. The resilience of a useful cache block is a

metric for the amount of disturbance by preempting tasks a useful cache block may suffer without causing an additional cache reload due to preemption. We also prove the correctness of this concept and provide a static program analysis to compute the resilience of the cache blocks.

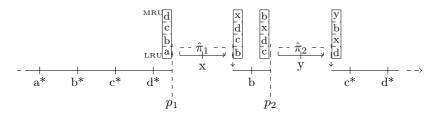

## **CRPD-Aware Response Time Analysis**

We show how to incorporate bounds on the cache-related preemption delays in the scheduling analysis for fixed-priority preemptive schedules. Nested preemption requires particular attention. A preempting task may not only evict cache blocks of one task but of all nestedly preempted tasks. Vice versa, a preempted task may suffer eviction not only by the directly preempting task but also by tasks preempting the preempting task. We first provide a thorough review of the existing approaches and then present a new and preciser analysis: the so-called ECB-Union. The new analysis derives upper bounds on the effect of all preempting tasks to the preempted task. In addition, we show how to eliminate spurious preemption scenarios to improve the schedulability results even further. We also present how to correctly consider mutual exclusive access to shared resources when considering CRPD explicitly.

# 1.2. Structure

The thesis is structured as follows: We introduce the framework of abstract interpretation (on which we base all program analyses) in Chapter 2. Chapter 3 provides further background needed for the understanding of this thesis. The formal model and explanation of the context switch costs and the cache-related preemption delay are given in Chapter 4 and an overview of the related work in Chapter 5. Chapter 6 presents the concept and the analysis of definitely-cached useful cache blocks, Chapter 7 the resilience analysis, and Chapter 8 the CRPD-aware schedulability analyses. An evaluation of the new approaches can be found in Chapter 9 and Chapter 10 concludes this thesis.

# **Publications Contributing to this Thesis**

Parts of the thesis have been published in peer-reviewed conferences, journals and workshops:

- Sebastian Altmeyer, Robert I. Davis, and Claire Maiza. Improved Cache related pre-emption aware response time analysis for fixed priority pre-emptive systems. In *Real-Time Systems* (to appear).

- Sebastian Altmeyer, Robert I. Davis, and Claire Maiza. Cache related pre-emption aware response time analysis for fixed priority pre-emptive systems. In *Proceedings of the 32nd IEEE Real-Time Systems Symposium*, (RTSS'11), pages 261–271, December 2011.

- Sebastian Altmeyer and Claire Maiza Burguière. Cache-related preemption delay via useful cache blocks: Survey and redefinition. J. Syst. Archit., 57:707-719, August 2011.

- Sebastian Altmeyer, Claire Maiza, and Jan Reineke. Resilience analysis: Tightening the CRPD bound for set-associative caches. In Proceedings of the ACM SIGPLAN/SIGBED 2010 conference on Languages, compilers, and tools for embedded systems, (LCTES '10), pages 153–162, April 2010.

- Sebastian Altmeyer and Claire Burguière. A new notion of useful cache block to improve the bounds of cache-related preemption delay. In *Proceedings of the 21st Euromicro Conference on Real-Time Systems*, (ECRTS '09), pages 109–118, July 2009.

- Claire Burguière, Jan Reineke, and Sebastian Altmeyer. Cacherelated preemption delay computation for set-associative caches pitfalls and solutions. In 9th Intl. Workshop on Worst-Case Execution Time (WCET) Analysis, July 2009.

# ABSTRACT INTERPRETATION

All exact science is dominated by the idea of approximation.

Bertrand Russell (1872 - 1970)

A program execution can be seen as a transformation of one state to another. The semantics of a program defines a) the set of states and b) how the program transforms a given state. Static program analysis [66] argues about certain properties of these states occurring during program execution, such as the sign of variables or the content of the cache memory. Many of these properties are undecidable in general such that the concrete semantics need to be approximated. Naturally, a program analysis must be sound in order to produce reliable results. Abstract interpretation [20, 21] provides means to design sound program analyses. In contrast to traditional program analysis that argues about program properties directly, abstract interpretation introduces a concrete and an abstract model of the semantics from which program properties can be derived. Correctness of the results is proven by showing that the abstract model is a sound approximation of the concrete model.

In this chapter, we introduce the basic notion of program analysis and abstract interpretation and provide the corresponding mathematical foundations. This chapter only serves as a basic introduction required for the understanding of this thesis. Further reading can be found in [21, 66, 44] and [75].

# 2.1. Program Analysis

Programs under examination are represented as *control-flow graphs*:

#### Definition 2.1 (Control-Flow Graph)

A control-flow graph (CFG) is a directed graph  $G = (V, E, p_s, p_e)$  with a finite set V of nodes, a set  $E \subseteq V \times V$  of edges, a start node  $p_s \in V$  and an end node  $p_e \in V$ . If  $(p_n, p_m) \in E$ ,  $p_n$  is a predecessor of  $p_m$  ( $p_m$  is successor of  $p_n$ ). Node  $p_s$  has no predecessor,  $p_e$  no successor. Note that we also refer to a node in the control flow graph as a program point.

We assume in addition that a CFG is connected and that  $p_e$  is the only end node, i.e., all nodes can be reached from start node  $p_s$  and all nodes may reach  $p_e$ . If a program has several exits  $p_e^1$  to  $p_e^n$  we enforce the second condition by introducing an artificial end node  $p_{e'}$  and corresponding edges  $(p_e^i, p_{e'})$ . A path within the control-flow graph is defined as follows:

#### Definition 2.2 (Path)

Let  $G = (V, E, p_s, p_e)$  be a CFG. A path  $\pi$  from node  $p_1$  to node  $p_k$  is a sequence of nodes  $\pi = [p_1, p_2, \dots, p_{k-1}, p_k]$  where  $\forall i : (p_i, p_{i+1}) \in E$ . The symbol  $\epsilon$  represents the empty path,  $\Pi$  the set of all paths and  $\pi_1 \cdot \pi_2$  concatenation of two paths.

# 2.1.1. Collecting Semantics

We describe the semantics of a program as transitions between program states. To this end, we define transfer function, path semantics, and the collecting semantics. Examples of program semantics are cache behavior and variable assignment.

# Definition 2.3 (Transfer functions)

Let  $G = (V, E, p_s, p_e)$  be a CFG and  $\mathbb{D}$  the set of program states. A transfer function  $tf: V \to (\mathbb{D} \to \mathbb{D})$  assigns the semantics of each node  $p \in V$ .

The transfer function (or transformer) defines the local semantics of each node of the CFG. The semantics of a complete path within the CFG is defined as the composition of the transfer functions.

# Definition 2.4 (Path Semantics)

The path semantics  $[\pi]_{tf_C}$  of a path  $\pi$  is a composition of a transfer function  $tf: V \to (\mathbb{D} \to \mathbb{D})$  along the path  $\pi$ :

$$[\pi]_{tf} = \begin{cases} id_{\mathbb{D} \to \mathbb{D}} & \text{if } \pi = \epsilon \\ [p_2, \dots, p_n]_{tf} \circ tf(p_1) & \text{if } \pi = [p_1, \dots, p_n] \end{cases}$$

Assume we are interested in the valuation of variables. A program state is defined as a function assigning each variable of the program a value and the transformer updates the program states according to the arithmetical operations of the program.

### **Sticky Collecting Semantics**

This far, we defined the semantics of a program always using transitions from one state to another. If we apply, for instance, the path semantics to an initial state, the semantics is only valid for this specific execution of the program path. However, we are usually interested in deriving information valid for a set of possible initial states. For this reason, we define the *collecting sticky semantics*.

#### Definition 2.5 (Sticky Collecting Semantics)

The sticky collecting semantics at node p for the set of initial states Init  $\subseteq \mathbb{D}$  is a function  $Coll: V \to 2^{\mathbb{D}}$  defined as

$$Coll(p) = \bigcup_{s \in Init} \left( \bigcup \{ [\pi]_{tf}(s) | \pi \in \Pi \land \pi = [p_s, \dots, p] \} \right)$$

The function  $\operatorname{Coll}(p)$  delivers all possible states at node p, i.e., all states that may arise at p during the execution of the program with all possible initial states  $s \in \operatorname{Init}$ . In the case of variable valuation the sticky collecting semantics delivers all values a variable may obtain at program point p. Such information can be used for instance to statically exclude division-by-zero exceptions.

## **Path-Based Collecting Semantics**

However, many program properties cannot be expressed using the sticky collecting semantics, at least not in a natural way. Liveness of variables for instance does not depend on the state at a program point p but on the paths reaching p. We therefore define the path-based collecting semantics [75].

# Definition 2.6 (Path-Based Collecting Semantics)

The path-based collecting semantics is the set of all paths ending in program point p (forward semantics)

$$Coll_{\Pi}^{\rightarrow}: V \rightarrow 2^{\Pi}$$

$$Coll_{\Pi}^{\rightarrow}(p) = \{ \pi \mid \pi \in \Pi \land \pi = [p_s, \dots, p] \}$$

(2.1)

or the set of all paths emanating from a program point p (backward semantics)

$$Coll_{\Pi}^{\leftarrow}: V \to 2^{\Pi}$$

$$Coll_{\Pi}^{\leftarrow}(p) = \{ \pi \mid \pi \in \Pi \land \pi = [p, \dots, p_n] \}$$

(2.2)

The path-based collecting semantics are also referred to as second-order semantics or trace semantics [75]. The liveness of a variable can be deduced from the backward path-based collecting semantics by checking if there exists at least one path on which the value of the variable is used.

Although some program properties require these collecting semantics, we can also define the path-based collecting semantics using the sticky collecting semantics. The concrete domain is the set of paths and the transfer function that appends, resp. prepends a program point to all paths  $tf_C^{\leftarrow/\rightarrow}$ :

$$tf^{\leftarrow/\rightarrow}: V \to (2^{\Pi} \to 2^{\Pi})$$

$$tf_{\pi}^{\rightarrow}(p)(S) := \{\pi \cdot p \mid \pi \in S\}$$

(2.3)

and

$$tf^{\leftarrow}(p)(S) := \{ p \cdot \pi \mid \pi \in S \} \tag{2.4}$$

The initial program state is the set of paths containing only the empty path  $\epsilon$ . Hence,

$$\operatorname{Coll}(p)^{\to} = \bigcup_{s \in \{\epsilon\}} \left( \bigcup \{ [\pi]_{tf^{\to}}(s) | \pi \in \Pi \land \pi = [p_s, \dots, p] \} \right)$$

$$= \{ \pi \mid \pi \in \Pi \land \pi = [p_s, \dots, p] \} = \operatorname{Coll}_{\Pi}^{\to}(p) \quad (2.5)$$

and

$$\operatorname{Coll}(p)^{\leftarrow} = \bigcup_{s \in \{\epsilon\}} \left( \bigcup \{ [\pi]_{tf^{\leftarrow}}(s) | \pi \in \Pi \land \pi = [p_s, \dots, p] \} \right)$$

$$= \{ \pi \mid \pi \in \Pi \land \pi = [p, \dots, p_e] \} = \operatorname{Coll}_{\Pi}^{\leftarrow}(p) \quad (2.6)$$

where  $\operatorname{Coll}(p)^{\to}$  is the original sticky collecting semantics as in Definition 2.5 and  $\operatorname{Coll}(p)^{\leftarrow}$  is the sticky collecting semantics used backwards, i.e., starting at the end node  $p_e$ .

This reduction allows us to consider only the sticky semantics for the following correctness proofs and to transfer the results to the path-based semantics. In the following, we thus only consider forward sticky collecting semantics.

# 2.2. Abstract Interpretation

Abstract interpretation is a formal, semantics-based framework to develop sound program analyses and to support the correctness proofs. It relates concrete semantics to abstract semantics. Within the framework of abstract interpretation, domains for the analyses are required to form partial orders to ensure that each subset of the domain has a least upper bound [23].

## **Preliminary Definitions**

First, we provide basic definitions needed in the remainder of this chapter.

#### Definition 2.7 (Partial Order)

A binary relation  $\sqsubseteq \subseteq \mathbb{D} \times \mathbb{D}$  over a set  $\mathbb{D}$  is a partial order, if and only if  $\forall a, b, c \in \mathbb{D}$  holds:

$$\begin{array}{c} a\sqsubseteq a & (Reflexivity) \\ a\sqsubseteq b\wedge b\sqsubseteq c\Rightarrow a\sqsubseteq c & (Transitivity) \\ a\sqsubseteq b\wedge b\sqsubseteq a\Rightarrow a=b & (Antisymmetry) \end{array}$$

The partial order  $\sqsubseteq$  is often used as a notion of precision. We say that  $a \in \mathbb{D}$  is at least as precise as  $b \in \mathbb{D}$  (or b approximates a) if  $a \sqsubseteq b$ .

## Definition 2.8 (Complete Lattice)

A complete lattice  $\mathbb{L}$  is a partially ordered set  $\mathbb{D}$ , where each subset  $\mathbb{S} \subseteq \mathbb{D}$  has a greatest lower bound ( $\square$ ) and a least upper bound ( $\square$ ). The elements  $\bot = \square \mathbb{D}, \top = \bigsqcup \mathbb{D}$  are referred to as the bottom and the top element of  $\mathbb{D}$ . A complete lattice  $\mathbb{L}$  is represented as a tuple  $\mathbb{L} = (\mathbb{D}, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$ . The operators  $\sqcup$  and  $\sqcap$  are called join or meet.

Note that each powerset domain  $2^{\mathbb{D}}$  together with subset ordering  $\subseteq$  forms a complete lattice  $(2^{\mathbb{D}}, \emptyset, \mathbb{D}, \subseteq, \bigcup, \bigcap)$ .

In the context of program analysis and abstract interpretation functions are often required to exhibit certain properties.

# Definition 2.9 (Monotonicity, Distributivity)

Let N with  $\sqsubseteq$  and M with  $\sqsubseteq'$  be partially ordered sets. A function  $f: N \to M$  is monotone, if and only if

$$\forall a,b \in N: a \sqsubseteq b \Rightarrow f(a) \sqsubseteq' f(b)$$

It is furthermore distributive, if and only if

$$\forall a, b \in N : f(a \sqcup b) = f(a) \sqcup' f(b)$$

#### Abstract Domain and its Relationship to the Concrete Domain

We now consider a powerset domain  $2^{\mathbb{D}_C}$  of concrete states  $\mathbb{D}_C$ . The collecting semantics of this domain delivers the most precise information any analysis may derive. In general, however, the collecting semantics are not computable or prohibitively large [43]. Hence, we strive for another description of the concrete states, namely a domain of abstract states  $\mathbb{D}_A$ . Abstract interpretation provides means to relate an abstract domain with the concrete one. We first argue about correct relations between both domains. In classical abstract interpretation, a Galois connection is demanded:

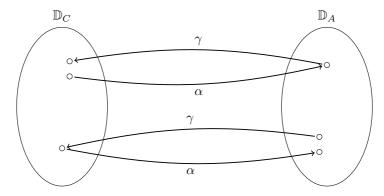

#### Definition 2.10 (Galois Connection)

Let  $(\mathbb{D}_C, \sqsubseteq)$  and  $(\mathbb{D}_A, \sqsubseteq)$  be partially ordered sets and  $\alpha : \mathbb{D}_C \to \mathbb{D}_A$ ,  $\gamma : \mathbb{D}_A \to \mathbb{D}_C$  two monotone functions. The tuple  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$  is a Galois connection, if and only if

$$\forall d \in \mathbb{D}_C : d \sqsubseteq \gamma(\alpha(d)) \tag{2.7}$$

and

$$\forall d \in \mathbb{D}_A : \alpha(\gamma(d)) \sqsubseteq d \tag{2.8}$$

We call the function  $\alpha$  abstraction and  $\gamma$  concretization.

A Galois connection establishes a relation between two domains [23]. Although one may lose precision by going back and forth between both domains, no elements are 'lost'. Applied to the concrete and abstract domain, if  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$  forms a Galois connection, abstraction and concretization are sound and  $\mathbb{D}_A$  is an actual representation of  $\mathbb{D}_C$ . Since an abstract domain typically exhibits a reduced size compared to the concrete domain, precision loss is often unavoidable. A weakness of the definition of Galois connection is that it allows to have two different abstract states to both represent the same set of concrete states. A stronger definition is the so called Galois insertion.

## Definition 2.11 (Galois Insertion)

A Galois connection  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$  is called Galois insertion, if and only if

$$\forall d \in \mathbb{D}_A : d = \alpha(\gamma(d))$$

Concretising and then abstracting must yield the original abstract state. Galois connections do not necessarily exist and are also not necessarily required for the correctness of an abstract domain. Instead, we require only Condition (2.7) of a Galois connection.

Figure 2.1.: Illustration of a Galois connection  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$ . The order of the domains defines the vertical position of each element: the higher an element is, the more precise it is.

#### Definition 2.12 (Sound Abstraction)

Let  $(\mathbb{D}_C, \sqsubseteq)$  and  $(\mathbb{D}_A, \sqsubseteq)$  be partially ordered sets and  $\alpha : \mathbb{D}_C \to \mathbb{D}_A$ ,  $\gamma : \mathbb{D}_A \to \mathbb{D}_C$  two monotone functions.  $\alpha$  and  $\gamma$  provide a sound abstraction if and only if

$$\forall d \in \mathbb{D}_C : d \sqsubseteq \gamma(\alpha(d))$$

This states that an element of the concrete domain d is conservatively approximated by  $\alpha(d)$ .

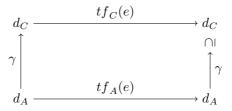

#### Correctness of the Abstract Transformer

In addition to a correct relation between two domains, we need to establish a correctness condition for the abstract transfer function

$$tf_A:V\to(\mathbb{D}_A\to\mathbb{D}_A)$$

which is also referred to as abstract transformer.

# Definition 2.13 (Local Consistency)

Given two functions  $tf_C: V \to (\mathbb{D}_C \to \mathbb{D}_C)$ ,  $tf_A: V \to (\mathbb{D}_A \to \mathbb{D}_A)$  and a concretization  $\gamma: \mathbb{D}_A \to \mathbb{D}_C$ . The two functions are locally consistent, if and only if

$$\forall d \in \mathbb{D}_A : \forall p \in V : (tf_C(p))(\gamma(d)) \subseteq \gamma((tf_A(p))(d))$$

Applied to a concrete and an abstract transformer, local consistency ensures that the abstract transformer preserves all states although it may

Figure 2.2.: Illustration of local consistency.

lose precision. In case of a Galois insertion, we can define the so-called best abstract transformer as  $\gamma \circ tf \circ \alpha$ . Note that the best transformer is often not computable in practice.

We can now define the abstract counterparts of the path semantics and the collecting semantics and prove the correctness. We simply have to replace the set-union  $\bigcup$  by greatest-lower bound operator  $\bigsqcup$  within the definitions and argue about an abstract domain.

## Definition 2.14 (Abstract Semantics)

The abstract path semantics  $[\pi]_{tf_A}$  of a path  $\pi$  is a composition of the transfer function  $tf_A: V \to (\mathbb{D} \to \mathbb{D})$  along the path:

$$[\pi]_{tf_A} = \begin{cases} id_{\mathbb{D} \to \mathbb{D}} & \text{if } \pi = \epsilon \\ [p_2, \dots, p_n]_{tf_A} \circ tf_A((p_1)) & \text{if } \pi = p_1, \dots, p_n \end{cases}$$

The abstract collecting semantics for the set of initial states  $Init_A \subseteq \mathbb{D}_A$  at node p is a function  $Coll_A: V \to 2^{\mathbb{D}}$  defined as

$$Coll_A(p) = \bigsqcup_{s \in Init_A} \left( \bigsqcup \{ [\pi]_{tf_A}(s) | \forall [p_s, \dots, p] \in \Pi \} \right)$$

In traditional (not abstract-interpretation based) program analysis, the abstract collecting semantics is referred to as meet-over-all paths (MOP) [66].

We prove the correctness of the abstract semantics with respect to the concrete semantics starting with the correctness of the abstract path semantics:

# Lemma 2.1 (Correctness of the abstract path semantics)

Given a Galois connection  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$ , the abstract path semantics is a sound over-approximation of the concrete path semantics if tf and  $tf_A$  are locally consistent.

$$\forall d \in \mathbb{D}_A : [\pi]_{tf_C}(\gamma(d)) \subseteq \gamma([\pi]_{tf_A}(d))$$

#### Proof

We prove the claim by induction over the length of the path  $\pi$ . In case of an empty path  $\epsilon$ , we have

$$[\epsilon]_{tf_C}(\gamma(d)) = \gamma(d)$$

$$= \gamma([\epsilon]_{tf_A}(d))$$

Induction hypothesis:

$$\forall d \in \mathbb{D}_A : [\pi]_{tf_G}(\gamma(d)) \subseteq \gamma([\pi]_{tf_A}(d))$$

holds for all  $\pi$  of length  $\leq l$ . Induction step  $\pi \to \pi' = (\pi, p_{l+1})$

$$\begin{split} [\pi']_{tf_C}(\gamma(d)) &= ([\pi']_{tf_C} \circ \gamma)(d) \\ &= ([\pi \cdot p_{l+1}]_{tf_C} \circ \gamma)(d) \qquad \qquad \pi' = \pi \cdot p_{l+1} \\ &= ([\pi]_{tf_C} \circ tf(p_{l+1}) \circ \gamma)(d) \qquad \qquad Def. \ 2.4 \\ &\subseteq ([\pi]_{tf_C} \circ \gamma \circ tf_A(p_{l+1}))(d) \qquad Local \ Consistency \\ &\subseteq (\gamma \circ [\pi]_{tf_A} \circ tf_A(p_{l+1}))(d) \qquad Ind. \ Hypothesis \\ &= (\gamma \circ [\pi \cdot p_{l+1}]_{tf_A})(d) \qquad Def. \ 2.14 \\ &= \gamma([\pi']_{tf_A})(d) \qquad \pi' = \pi \cdot p_{l+1} \end{split}$$

Correctness of the abstract collecting semantics remains to be shown. We therefore need to show that the abstract collecting semantics is a sound over-approximation of the concrete collecting semantics.

Lemma 2.2 (Correctness of the abstract collecting semantics) Given a Galois connection  $(\mathbb{D}_C, \alpha, \gamma, \mathbb{D}_A)$ , the abstract collecting semantics is a sound over-approximation of the concrete collecting semantics

$$\forall p \in V : Coll(p) \subseteq \gamma(Coll_A(p))$$

if tf and tf<sub>A</sub> are locally consistent and  $Init_A$  is an over-approximation of  $Init\ (\gamma(Init_A) \supseteq Init)$ .

## Proof

$$Coll(p)$$

$$= \bigcup_{s \in Init} \left( \bigcup \{ [\pi]_{tf_C}(s) | \forall [p_s, \dots, p] \in \Pi \} \right) \qquad Def. \ 2.5$$

$$\subseteq \bigcup_{s \in Init_A} \left( \bigcup \{ [\pi]_{tf_C}(\gamma(s)) | \pi = [p_s, \dots, p] \in \Pi \} \right) \qquad \gamma(Init_A) \supseteq Init_A$$

$$\subseteq \bigcup_{s \in Init_A} \left( \bigcup \{ \gamma([\pi]_{tf_A}(s)) | \pi = [p_s, \dots, p] \in \Pi \} \right) \qquad Lemma \ 2.1$$

$$\subseteq \bigcup_{s \in Init_A} \gamma\left( \bigcup \{ [\pi]_{tf_A} | \pi = [p_s, \dots, p] \in \Pi \} \right) \qquad Monotonicity$$

$$\subseteq \gamma\left( \bigcup_{s \in Init_A} \left( \bigcup \{ [\pi]_{tf_A}(s) | \pi = [p_s, \dots, p] \in \Pi \} \right) \right) \qquad Monotonicity$$

$$= \gamma(Coll_A(p)) \qquad Def. \ 2.14$$

Finally, we can formulate conditions each sound abstraction of the concrete semantics must fulfill:

- the abstract domain  $\mathbb{D}_A$  is a partially ordered set,

- $\alpha$  and  $\gamma$  form a sound abstraction of the abstract domain, and

- $\bullet$   $\,tf$  and  $tf_A$  must be locally consistent.

# 2.3. Fixed-Point Analysis

Definition 2.5 and 2.14 define the (abstract) semantics of a program. In general however even the abstract collecting semantics is not efficiently computable [43]. The number of paths may be infinite or just too large in practice. Hence, the *minimal-fixed-point solution (MFP)* is computed [46, 43].

## Definition 2.15 (Minimal-Fixed-Point Solution (MFP))

The minimal fixed-point (MFP) MFP :  $V \to (\mathbb{D} \to \mathbb{D})$  is the least fixed-point of the recursive equation system

$$MFP(p) = \begin{cases} \bot & p = p_s \\ \bigsqcup \{tf(p)(MFP(p_m)) \mid (p_m, p) \in E\} & p \neq p_s \end{cases}$$

We now describe the conditions an abstraction must fulfill to ensure that i) the MFP is computable and ii) it results in an approximation of the collecting semantics  $Coll_A$ .

#### Theorem 2.1 (Knaster-Tarski [87])

In a complete lattice  $\mathbb{L}$ , each monotone function  $f: \mathbb{L} \to \mathbb{L}$  has a minimal fixed-point.

According to Theorem 2.1, a minimal fixed-point as defined by MFP exists, if the transfer function tf is monotone [87].

## Definition 2.16 (Ascending Chain)

An ascending chain x is a sequence of elements  $x_i \in \mathbb{D}$  of a partially ordered set  $(\mathbb{D}, \sqsubseteq)$ , such that  $\forall i : x_i \sqsubseteq x_{i+1}$ . A chain stabilizes if  $\exists j : \forall l > j : x_l = x_j$ .

## Theorem 2.2 (Kleenes Fixed-Point Theorem)

Let  $\mathbb{L} = (\mathbb{D}, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$  be a lattice and  $f : \mathbb{D} \to \mathbb{D}$  be a monotone function. If all ascending chains in  $\mathbb{L}$  finally stabilize, then

$$\exists k : \forall l > k : f^l(\bot) = f^k(\bot)$$

and  $f^k(\perp)$  is the least fixed-point of f.

Kleenes' Theorem 2.2 defines the properties under which the iterative application of a function finally stabilizes and results in the minimal fixed-point. Note that there are several algorithms implementing the MFP Solution and therefore solving the data-flow problem. A detailed discussion on this topic can be found in [56].

Monotonicity holds for probably all meaningful transfer functions. However, there are some lattices where ascending chains do not stabilize. A prominent example is the *interval analysis* which tries to predict a value interval [a,b] for each program variable v such that  $v \in [a,b]$ . For such analyses, widening and narrowing operators can be defined to restore computability [22]. A widening-operator sets the data-flow value to an upper bound (in case of interval analysis  $\infty$ ) such that the algorithm results in a—possibly not-minimal but—valid fixed-point. Narrowing may then be used to reduce the pessimism introduced by widening.

So far, we only discussed computability of the MFP solution. The next theorems argue about soundness and precision of MFP compared to  $Coll_A$ . Remember that the precision is defined by the relation  $\sqsubseteq$  (see Definition 2.7).

#### Theorem 2.3 (Coincidence)

Let  $\mathbb{L} = (\mathbb{D}, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$  be a lattice and  $f : \mathbb{D} \to \mathbb{D}$  be a monotone function. If all ascending chains in  $\mathbb{L}$  finally stabilize, then

$$\forall p \in V : Coll_A(p) \sqsubseteq MFP(p)$$

The Coincidence-Theorem 2.3 states that MFP approximates  $Coll_A$ , i.e.,  $Coll_A \sqsubseteq MFP$  for all possible initial states and all nodes. According to Theorem 2.4 equality is given, if the transfer function is distributive [46].

## Theorem 2.4 (Kildall [46])

Let  $\mathbb{L} = (\mathbb{D}, \bot, \top, \sqsubseteq, \sqcup, \sqcap)$  be a lattice,  $f : \mathbb{D} \to \mathbb{D}$  be a monotone function and . If f is furthermore distribute, then

$$\forall p \in V : Coll_A(p) = MFP(p)$$

(assuming that each node  $p \in V$  is reachable from the starting node  $p_s$ ).

We can conclude that a transfer function needs to be monotone in order to be able to compute an approximation of the collecting semantics. If all ascending chains within the corresponding lattice stabilize, fixed-point iteration will result in a correct approximation of the  $Coll_A$ . If not, widening and/or narrowing operators must be defined. If in addition, the transfer function is distributive, MFP equals  $Coll_A$ .

# BACKGROUND

If I have been able to see further, it was only because I stood on the shoulders of giants.

Sir Isaac Newton (1643 - 1727)

This chapter presents the basics of different fields necessary for the understanding of this thesis: real-time scheduling, caches and timing analysis. Nevertheless, it is not meant as a general introduction but presents only the relevant information and notation. Parts familiar to the reader can be skipped.

# 3.1. Real-Time Scheduling

Embedded systems typically feature more tasks than processors. Thus, a *scheduler* is employed to distribute the available processing time to the tasks. In contrast to schedulers in general-purpose OS, where load-balancing or fairness is a main objective, real-time schedulers are faced with timing constraints such as deadlines of tasks. Depending on the penalty assigned to a deadline miss, real-time systems are divided into hard or soft. When a deadline miss is considered a complete failure of the system, it is considered a *hard* real-time system, when some deadline misses are tolerable, it is considered a *soft* real-time system.

Real-time scheduling denotes a large research area with plenty of

19

different approaches and methods of which this section only presents the subset relevant for this thesis: uniprocessor preemptive priority-driven scheduling with static priority assignment as widely used in real-time systems. For a general overview on real-time scheduling see [19].

# 3.1.1. Sporadic Task Model

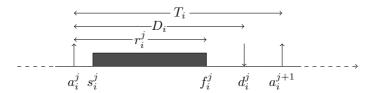

We assume a fixed set  $\Gamma$  of n tasks  $\Gamma = \{\tau_1, \ldots, \tau_n\}$  to be executed on a single processor. Each task is assigned a worst-case execution time  $C_i$ , a relative deadline  $D_i$  and minimal inter-arrival time or period  $T_i$  with release jitter  $J_i$ . Each instance of task execution is called a job. Arrival

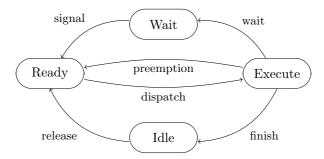

Figure 3.1.: State transitions of a task

time  $a_i^j$  denotes the time at which the *j*-th instance of task  $\tau_i$  (or job *j* of  $\tau_i$ ) becomes ready to execute, and start time  $s_i^j$  the time the job is dispatched by the scheduler and starts to execute. Figure 3.1 shows the states and transitions of a task. The next job of task  $\tau_i$  arrives at the earliest after a time span  $T_i$  minus jitter  $J_i$ :

$$a_i^{j+1} \ge a_i^j + T_i - J_i \tag{3.1}$$

Deadline  $d_i^j$  of a job is relative to its arrival time:

$$d_i^j = a_i^j + D_i (3.2)$$

Finishing time  $f_i^j$  of a job denotes the time at which this job completes execution and the response time  $r_i^j$  denotes the time span from job arrival to job completion:

$$r_i^j = f_i^j - a_i^j \tag{3.3}$$

Response time of a task is given by the worst-case response time of its jobs:

$$R_i = \max_j \{r_i^j\} \tag{3.4}$$

Worst-case execution time  $C_i$  denotes the maximal execution demand without preemption cost. The fraction of time a task requires the processor is denoted as the task's utilization:

$$U_i = C_i/T_i \tag{3.5}$$

*Utilization* of a task set  $\Gamma = (\tau_1, \dots, \tau_n)$  is the sum of the utilizations of all tasks:

$$U_{\Gamma} = \sum_{i=1}^{n} C_i / T_i \tag{3.6}$$

A task  $\tau_j$  is referred to as *schedulable* if each of its jobs finishes before their deadline:

$$R_i \le D_i - J_i \Leftrightarrow \tau_i \text{ schedulable}$$

(3.7)

A task set  $\Gamma$  is said to be schedulable if each task  $\tau_i \in \Gamma$  is schedulable.

Table 3.1.: Task model properties

| $\Gamma = \{\tau_1, \dots, \tau_n\}$ | Task set of $n$ tasks        |

|--------------------------------------|------------------------------|

| C                                    | Execution Time Demand (WCET) |

| T                                    | Minimal Inter-arrival Time   |

| D                                    | Deadline                     |

| J                                    | Release Jitter               |

| U                                    | Utilization                  |

| $\overline{s}$                       | Starting Time                |

| a                                    | Arrival Time                 |

| f                                    | Finishing time               |

| r                                    | Response Time (Job)          |

| R                                    | Response Time (Task)         |

Figure 3.2.: Illustration of the sporadic task model and the associated variables

Table 3.1 summarizes and Figure 3.2 illustrates the parameters associated with each task/job. We assume independent tasks but weaken

this restriction and allow tasks to access  $mutual\ exclusive$  sections via semaphores in Section 3.1.3

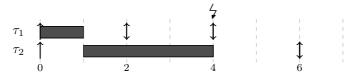

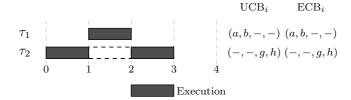

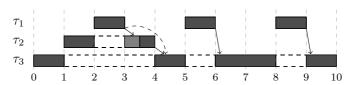

#### Why preemption?

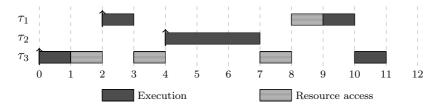

Tasks can be executed either preemptively or non-preemptively. In a non-preemptively scheduled system, once started, each task runs to completion. In a preemptively scheduled system, a task's execution can be temporarily interrupted to execute another task. Preemptive schedules are potentially more powerful, i.e, some task sets are only schedulable preemptively. Tasks with short deadline usually can not postpone their execution until completion of the currently running task. See the task set shown in Figure 3.3.

(a) Preemptive Execution, no missed Deadlines.

(b) Non-Preemptive Execution, Deadline Miss of task  $\tau_1$  at 4.

Figure 3.3.: Preemptive versus Non-preemptive Scheduling: task set  $\{\tau_1, \tau_2\}$  with  $C_1 = 1$ ,  $D_1 = T_1 = 2$  and  $C_2 = 3$ ,  $D_2 = T_2 = 6$ .

# 3.1.2. Priority-Driven Scheduling

A priority-driven scheduler always executes the task  $\tau_i$  with the highest priority  $pr(\tau_i)$  among all tasks that are ready to execute. Priorities are assigned either statically or dynamically. Earliest deadline first (EDF) scheduling [53] and deadline monotonic (DM) scheduling—also called Rate Monotonic (RM) [53] in case of implicit deadlines  $(\forall_i : D_i = T_i)$ —are the main representatives for dynamic and static assignments, respectively. They are also optimal among scheduling algorithm of their class in the following sense: if there exists a feasible schedule with static, resp., dynamic priority assignment, deadline monotonic, resp., earliest deadline

first finds one too. Note that these optimality results only hold for preemptive systems assuming negligible preemption cost.

## Earliest Deadline First (EDF)

Earliest deadline first scheduling [53] always executes the task with the closest deadline. It maintains a priority queue of the ready tasks ordered by the proximity of each task's deadline. For the special case of implicit deadlines, EDF is always able to schedule a task set if the utilization of the task set is less than or equal to 1:

$$U_{\Gamma} \le 1 \Leftrightarrow \Gamma \text{ schedulable}$$

(3.8)

In the general case with explicit deadlines, the schedulability test is more complex [40]. For each time span L, the requested processor time must be less than or equal to L:

$$\forall L > 0: \sum_{i} \lfloor (L + T_i - D_i) / T_i \rfloor C_i \le L \Leftrightarrow \Gamma \text{ schedulable}$$

(3.9)

Both schedulability tests are necessary and sufficient.

## Deadline Monotonic (DM)

Deadline monotonic scheduling [52, 100] assigns task priorities in order of increasing deadlines, giving the task with the shortest deadline the highest priority. We assume w.l.o.g. that task indices express the priority order:

$$D_1 \le D_2 \le D_3 \le \dots \le D_n \tag{3.10}$$

and

$$pr(\tau_1) > pr(\tau_2) > pr(\tau_3) > \dots > pr(\tau_n)$$

(3.11)

For implicit deadlines  $(T_i = D_i)$ , two linear-time sufficient schedulability tests based on the utilization of the task set exist. The first one was presented by Liu and Layland [53]:

$$U_{\Gamma} \le n(2^{1/n} - 1) \Rightarrow \Gamma \text{ schedulable}$$

(3.12)

with

$$\lim_{n \to \infty} n(2^{1/n} - 1) = \ln(2) \approx 0.6932 \tag{3.13}$$

The second schedulability test is the *hyperbolic bound* test by Bini et al. [15]:

$$\prod_{i=1}^{n} (U_i + 1) \le 2 \Rightarrow \Gamma \text{ schedulable}$$

(3.14)

Note that both tests are only valid for implicit deadlines and are only sufficient, not necessary. For a performance evaluation of RM scheduling based on randomly generated tasks see [51].

#### Response Time Analysis

A sufficient and necessary test for static priorities is the response time analysis [8, 41, 25]. Equation (3.7) states that a task is schedulable, if its worst-case response time  $R_i$  is less than or equal to its deadline  $D_i$  less jitter  $J_i$ .

The response time  $R_i$  of a task necessarily contains its execution time  $C_i$ . In addition,  $\tau_i$  suffers interference from tasks with higher priority than  $\tau_i$ . Let  $\tau_j$  be a task with priority higher than  $\tau_i$ . Within the response time  $R_i$ ,  $\tau_j$  executes at most  $\left\lceil \frac{R_i + J_j}{T_j} \right\rceil$  times, each time for at most  $C_j$ . Hence, the response time  $R_i$  of task  $\tau_i$  is given by:

$$R_i = C_i + \sum_{\forall j \in \text{hp}(i)} \left\lceil \frac{R_i + J_j}{T_j} \right\rceil (C_j)$$

(3.15)

where  $hp(\tau_i)$  denotes the set of tasks with higher priority than  $\tau_i$ . The response time  $R_i$  appears on the left-hand side and on the right-hand side. As the right-hand side is monotonically increasing in  $R_i$ , a fixed-point computation of  $R_i$  based on Equation (3.15) can be defined as follows:

$$R_i^0 = C_i (3.16)$$

$$R_i^{l+1} = C_i + \sum_{\forall j \in \text{hp}(i)} \left\lceil \frac{R_i^l + J_j}{T_j} \right\rceil (C_j)$$

(3.17)

Eventually, for each task, the fixed-point computation either stabilizes, i.e.,  $R_i^l = R_i^{l+1}$ , or the response time  $R_i^l$  of one task exceeds the deadline  $R_i > D_i$ . In the first case, we can conclude that each job of task  $\tau_i$  will finish before its deadline, so each task is schedulable. In the second case, we can conclude that at least one job of task  $\tau_j$  may miss its deadline, so the task set is not schedulable.

Note that the response time analysis is valid for any *static priority* assignment and also for explicit deadlines. It exhibits pseudo-polynomial runtime (compared to linear runtime for the Utilization and Hyperbolic bound), but forms a sufficient and necessary schedulability test (under the assumption of negligible context switch costs).

#### 3.1.3. Mutual Exclusion

In this section, we extend the sporadic task model by mutual exclusive accesses to shared resources. A sequence of a task  $\tau_i$  accessing such a shared resource is called *critical section*.

To ensure consistency of shared resources, at most one task can access a resource at a time. Semaphores are typically used to implement this  $mutually\ exclusive$  access: Each shared resource is assigned a semaphore  $S_i$  that implements two primitive operations

wait( $S_i$ ): a task requests access to a shared resource. If the resource's semaphore  $S_i$  is available, a task can enter its critical section and access the shared resource, while locking  $S_i$ . If  $S_i$  is not available, the task blocks on  $S_i$  and suspends its execution.

**signal**( $S_i$ ): a task that previously accessed a shared resource assigned to semaphore  $S_i$  finishes its critical section and unlocks  $S_i$  again.

Each critical section accessing a shared resource with semaphore  $S_i$  thus begins with  $wait(S_i)$  and ends with  $signal(S_i)$ . Task states and transitions are depicted in Figure 3.4.

Figure 3.4.: State transitions of a task with shared resources

# **Priority Inversion Problem**

Each task  $\tau_i$  that shares a resource with a task  $\tau_j$  with lower priority inevitably may suffer delay of the length of the critical section of  $\tau_j$  accessing the shared resource. *Priority inversion* denotes the situation where a task's execution is prolonged by the execution of a task with lower priority even though both tasks do *not* share a common resource. See Figure 3.5 for an example. Task  $\tau_1$  and  $\tau_3$  both access a shared

resource guarded by semaphore S. Task  $\tau_3$  first enters its critical section and locks S. Task  $\tau_1$  is activated at time 2, starts to executes but blocks on S at time 3. Now  $\tau_3$  resumes execution again, but is preempted by  $\tau_2$  at time 4. So, the  $\tau_1$  is not only delayed by the critical section of  $\tau_3$  but also by the execution time of  $\tau_2$ . Several protocols have been

Figure 3.5.: Priority inversion problem

proposed to solve the priority inversion problem. We will now shortly present the most prominent protocols: priority inheritance, priority ceiling and stack resource protocol. As only the latter one is able to handle dynamic priorities, we restrict the following description to static priority assignment.

| $\overline{\mathrm{SR}_i}$ | shared resource                                              |  |  |  |  |

|----------------------------|--------------------------------------------------------------|--|--|--|--|

| $S_i$                      | semaphore guarding $SR_i$                                    |  |  |  |  |

| $Access(SR_i)$             | set of tasks accessing shared resource $SR_i$                |  |  |  |  |

| pr                         | nominal priority                                             |  |  |  |  |

| $\widehat{pr_i}$           | active priority with $\widehat{pr_i} \geq pr_i$              |  |  |  |  |

| $C(S_i)$                   | Ceiling priority of semaphore $S_i$ (PCP)                    |  |  |  |  |

| $S^*$                      | Currently locked semaphore with highest $C(S)$ (PCP)         |  |  |  |  |

| $cs_{i,k}$                 | critical section of task $\tau_i$ accessing resource $SR_k$  |  |  |  |  |

| $C_{i}^{\mathrm{SR}_{k}}$  | worst-case execution time of the critical section $cs_{i,k}$ |  |  |  |  |

Table 3.2.: Shared resources: notation and terminology

## Priority Inheritance Protocol (PIP)

To prevent priority inversion, the priority inheritance protocol (PIP) [77] increases the priority of a blocking task  $\tau_i$  to the priority of the task with the highest priority currently blocked by  $\tau_i$ . It therefore assigns each task an active priority  $\widehat{pr_i}$  initially set to the nominal priority  $pr_i$  (the one assigned by the scheduling algorithm, e.g. deadline monotonic).

The protocol works as follows:

- the task  $\tau_i$  with the highest active priority  $\widehat{pr_i}$  among all ready tasks is executed.

- when the running task  $\tau_i$  requests a semaphore  $S_l$ :

- if  $S_l$  is free,  $\tau_i$  locks  $S_l$  and enters its critical section.

- if  $S_l$  is blocked by another task  $\tau_j$ ,  $\tau_j$  inherits the priority of  $\tau_i$ :  $\widehat{pr_j} := \widehat{pr_i}$ .

- when a task  $\tau_i$  exits its critical section, it releases the corresponding semaphore  $S_l$  and:

- if  $\tau_i$  blocks no other task, the active priority of  $\tau_i$  is set to the nominal priority  $\widehat{pr_i} := pr_i$ .

- otherwise, the active priority of  $\tau_i$  is set to the active priority of the task  $\tau_j$  with the highest priority of all tasks still blocked by  $\tau_i$ :  $\widehat{pr_i} := \widehat{pr_j}$ .

Note that priority inheritance is transitive.

Although PIP prevents priority inversion, a task may still suffer substantial delay by the blocking time of lower-priority tasks. In the worst-case,  $\tau_i$  may suffer m blocking delays where m denotes the number of shared resources  $\tau_i$  accesses. Such a situation is called chained blocking. In addition, nested shared resources may lead to a deadlock situation [19].

# Priority Ceiling Protocol (PCP)

Priority Ceiling Protocol (PCP) by Sha et al. [77] improves over PIP in the sense that a) each task can be delayed by at most one critical section and b) deadlocks are prevented. Instead of assigning priorities only to tasks, each semaphore  $S_i$  is statically assigned a ceiling priority  $C(S_i)$ . The ceiling priority is the highest priority of any task accessing the shared resource guarded by  $S_i$ :

$$C(S_i) = \max\{pr_j \mid \tau_j \in \text{Access}(SR_i)\}$$

(3.18)

where  $Access(SR_i)$  denotes the set of tasks accessing shared resource  $SR_i$ . In addition, PCP keeps track of the currently locked semaphore  $S^*$  with the highest ceiling priority  $C(S_l)$  of all locked semaphores. The protocol prevents a task  $\tau_i$  from entering a critical section guarded by  $S_l$  not only if  $S_l$  is locked, but also if there is any semaphore currently locked that could lead to blocking of  $\tau_i$ .

The protocol works as follows:

- the task  $\tau_i$  with the highest active priority  $\widehat{pr_i}$  among all ready tasks is executed.

- when the running task  $\tau_i$  requests a semaphore  $S_l$ :

- if  $\widehat{pr_i} > C(S^*)$ ,  $\tau_i$  locks  $S_l$  and enters its critical section.

- otherwise  $\tau_i$  is blocked by another task  $\tau_j$  holding semaphore  $S^*$  and  $\tau_j$  inherits the priority of  $\tau_i$ :  $\widehat{pr_j} := \widehat{pr_i}$ .

- when a task  $\tau_i$  exits its critical section, it releases the corresponding semaphore  $S_l$  and updates  $S^*$ . Furthermore,

if  $\tau_i$  blocks no other task, the active priority of  $\tau_i$  is set to the nominal priority  $\widehat{pr_i} := pr_i$ .

otherwise, the active priority of  $\tau_i$  is set to the priority of the task  $\tau_j$  with the highest priority of all tasks still blocked by  $\tau_i$ :  $\widehat{pr_i} := \widehat{pr_j}$ .

With PCP, the maximal blocking delay a task  $\tau_i$  may suffer is bounded by the maximal execution time  $C_j^{\text{SR}_k}$  of a critical section  $\text{SR}_k$  of a lower priority task  $\tau_j$  that shares a common resource  $\text{SR}_k$  guarded by a semaphore with ceiling priority  $C(S_k)$  higher than or equal to the priority  $\tau_i$ :

$$B_i = \max\{C_j^{\text{SR}_k} \mid pr_j < pr_i \land C(S_k) \ge pr_i\}$$

(3.19)

## Stack Resource Protocol (SRP)

The stack resource protocol (SRP) [9] denotes a set of extensions to PCP. SRP is applicable in case of dynamic priorities, allows for multi-unit resources, i.e., resources that enable up to l parallel accesses, and enables sharing of runtime stack resources. In the simple case we consider here, where we are only interested in static priority assignment and binary semaphores that are either locked or free, the improvement of SRP merely breaks down to the advantage that SRP exhibits less context switches than PCP. This, however, can also be achieved in the priority ceiling protocol by adding the following rules:

- When a task enters a critical section, its priority is set to  $C(S^*)$ .

- When a task leaves the critical section, its former priority is restored.

Thus, a task  $\tau_i$  with priority less than or equal to  $C(S^*)$  is prevented from being activated and not only from entering a critical section. This results in less context switches besides otherwise equal behavior compared to the original priority ceiling protocol.

#### Mutual Exclusion and Response Time Analysis

The response time Equation (3.15) can be extended as follows to include the blocking delay  $\tau_i$  may suffer:

$$R_i = C_i + B_i + \sum_{\forall j \in \text{hp}(i)} \left\lceil \frac{R_i + J_j}{T_j} \right\rceil (C_j)$$

(3.20)

with  $B_i$  defined by Equation (3.19).

# 3.2. Memory Hierarchy and Caches

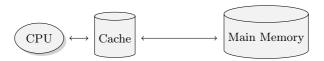

Fast and large memory are desirable, but infeasible due to technical (and economical) limitations. Instead, existing storages are either large and slow or small and fast. To emulate a memory which is fast and large at the same time, *memory hierarchies* were introduced based on memories with varying speeds and sizes: Small but fast memories on top, slower but larger memories below. Each memory level contains a subset of the data stored in the level below. Scratchpads, caches or buffers are examples for such intermediate memories. See Figure 3.6 for a simple memory hierarchy of an embedded architecture.

Figure 3.6.: Typical memory hierarchy often to be found in embedded systems

# 3.2.1. Principle of Locality

To decide which memory blocks to store, a memory hierarchy utilizes a heuristic known as the *locality principle* [26]:

**Spatial Locality** neighboring memory blocks are likely to be accessed contemporary.

**Temporal Locality** recently accessed memory blocks are likely to be accessed in the near future again.

The rationale behind these locality principles is the exploitation of common characteristics of task executions. Memory accesses are not uniformly distributed over a task's data. Sequential code alignment and clustering of data (arrays etc.) increase the likelihood of accessing neighboring memory blocks. Loop structures increase the likelihood of reusing recently accessed memory blocks. Spatial locality is realized by storing not only the currently accessed data but larger chunks of contiguous memory containing the accessed blocks. Temporal locality is realized by storing recently accessed data.

In the following, we focus on uni-level processor caches common in typical embedded systems. For an overview on memory hierarchies and caches, we refer to Hennesy and Patterson [37]. We also skip description of memory management units and virtual memory management, as both concepts are not common in hard real-time systems.

#### 3.2.2. Processor Caches

Typically located on the die of the microprocessor, processor caches serve data much faster than the main memory which is connected by the memory bus. Caches operate completely transparently to the processor semantics, only influencing timing behavior and performance. On a memory access (no matter if read or write), data is requested from the cache. In case the accessed memory block is resident in cache, a situation called cache hit, the processor directly reads from/writes to cache. Only in case of a cache miss, i.e., data not resident in cache, the requested data is retrieved from the main memory and then loaded to the cache. There are three types of cache misses [38]:

- **Compulsory Misses** misses on the first access of a memory block. As caches are initially empty, the first access to a datum always inflicts a cache miss.

- **Capacity Misses** misses due to the limited cache capacity. Such misses occur if the amount of accessed data exceeds the cache size.

- **Conflict Misses** misses due to an unbalanced cache usage, i.e., misses due to eviction in one cache set, while cache lines of other sets are still empty.

The delay to retrieve data from main memory is referred to as *cache-miss* penalty or *block-reload time*.

#### **Cache Organization**

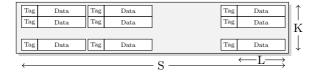

To implement spatial locality, caches do not only store the accessed data, but load memory blocks of line size L usually substantially larger than the accessed element. Caches are partitioned into S cache sets, where each memory block (of size L) maps to exactly one of the cache sets. Each cache set in turn may contain up to K different memory blocks at once, where K is referred to as the associativity of the cache. Cache size is thus given by  $L \cdot S \cdot K$ . Such a cache is called a set-associative

Table 3.3.: Cache parameter and domains

| Line Size                                                            | $L \in \mathbb{N}$                          |

|----------------------------------------------------------------------|---------------------------------------------|

| Associativity                                                        | $K \in \mathbb{N}$                          |

| Number of Sets                                                       | $S \in \mathbb{N}$                          |

| Cache Size                                                           | $CS \in \mathbb{N}; CS = L \cdot S \cdot K$ |

| Policy                                                               | $P \in \{LRU, FIFO, PLRU\}$                 |

| Cache-Set State                                                      | $\zeta \in Z$                               |

| Set of Memory Blocks                                                 | M                                           |

| Invalid Line                                                         | $\perp$                                     |

| Content of a cache Line                                              | $M_{\perp} = M \cup \{\perp\}$              |

| Cache-Set Update                                                     | $t^P: M \times \zeta^P \to \zeta^P$         |

| Content of a Cache Set                                               | $\overline{\zeta} \in 2^{M_{\perp}}$        |

| Number of misses on path $\pi$ and on an initial cache state $\zeta$ | $miss:\Pi\times Z\to\mathbb{N}$             |

| Number of hits on path $\pi$ and on an initial cache state $\zeta$   | $hits:\Pi\times Z\to\mathbb{N}$             |

cache. See Figure 3.7. The set of all memory blocks is denoted by M. We introduce symbol  $\perp$  to represent empty or invalid cache lines.

There are two special cases of set-associative caches:

**Direct-Mapped Caches (**K=1**)** Each memory block can reside in exactly one cache line. Direct-mapped caches exhibit low hardware implementation cost. However, memory accesses are usually not uniformly distributed over all cache sets resulting in unnecessary conflict misses.

Fully-Associative Caches (K = S) Each memory block can reside in any cache line. Fully-associative caches only need to evict data if all cache lines of the whole cache are filled. Hardware implementation of such caches is costly so that only small caches are fully-associative.

Figure 3.7.: Cache organization on a K-way set associative cache

#### Cache Tags and Block Addresses

To identify which parts of the main memory are currently cached, caches must store not only the actual data but also tags to identify the memory address the data belongs to.

A tag is the smallest possible portion of the  $memory\ address$  sufficient to reconstruct the original address. As caches always store blocks of size L, the last  $\log(L)$  bits of the address do not need to be considered. The same holds for the previous  $\log(S)$  bits, as this part of the address can be reconstructed from the index of the cache set in which data is stored. The remaining bits form the tag of an address and need to be stored together with the data. See Figure 3.8.

Figure 3.8.: Address Computation

# Write-Through vs. Write-Back

On a write access, a changed datum must be written back to the main memory eventually. When to perform this write back depends on the write policy. The two alternatives are:

Write-Through datum is directly written to main memory, or,

**Write-Back** datum is marked as *dirty* and written to main memory when evicted from cache.

Write policies form another trade-off between hardware cost and performance. A write-back cache requires book-keeping of all dirty cache lines. However, it benefits from fewer memory accesses compared to a write-through cache, which sends data to main memory on each write access. Another decision related to write accesses is the question whether or not

to store the written data in the cache. The alternatives are called writeallocate and no write-allocate. Typical combinations are write-through with no write-allocate (as each write incurs a main memory access) and write-back with write-allocate.

For timing-critical embedded systems, write-through caches are considered beneficial as the point in time of each main-memory write depends statically on the instruction. Write-back caches do not allow for a precise determination of these memory-writes—or at least, no precise analysis is known yet.

# 3.2.3. Replacement Policy

Eventually, all ways of a cache set are filled. On a cache miss, the currently accessed element has to be stored in the cache while evicting another one. Which element to replace is determined by the replacement policy. The most common replacement policies are least-recently used (LRU), first-in first-out (FIFO) and pseudo least-recently used (PLRU). Note that no replacement policy is needed for direct-mapped caches as each set has only one way and each memory block maps to a unique cache position. In the following, we refer to a position in a cache as the age of a cache block. These are always meant as logical concepts and do not refer to the physical position in the cache hardware.

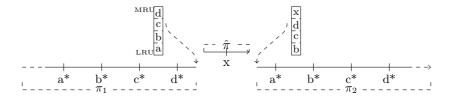

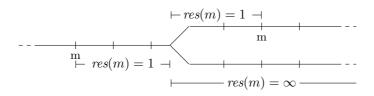

## Least-Recently Used (LRU)

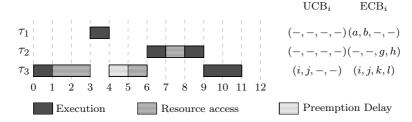

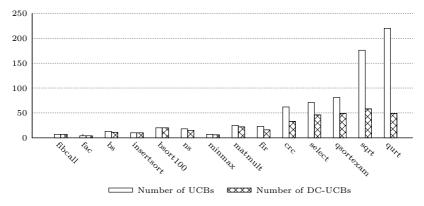

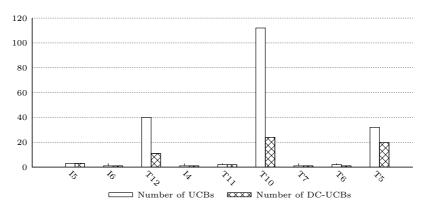

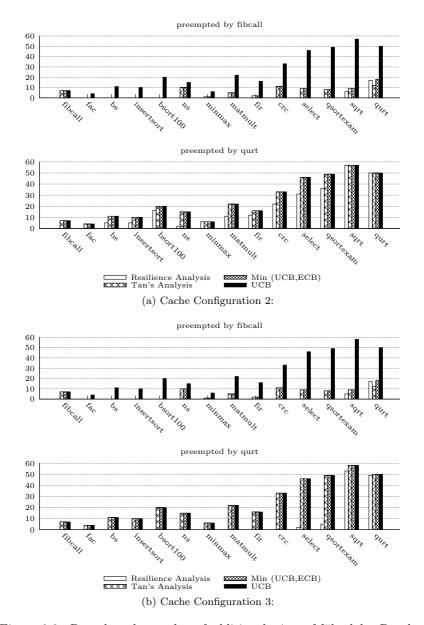

LRU policy keeps a list of cached memory blocks ordered by the last use of each memory block. To keep this order, it conceptually assigns each cached memory block an age indicating its position in the order. The most-recently used element has age 0, the least-recently used age K-1. It treats misses and hits uniformly. A property considerably useful for timing analysis and predictability of a cache. Starting with a completely unknown initial cache state, precise information about the cache content (and the age of each memory block) can be derived after accessing K different memory blocks. LRU caches are predominant in academia, but