Saarland University Faculty of Natural Sciences and Technology I Department of Computer Science

PhD Thesis

### Cache based Optimization of Stencil Computations An Algorithmic Approach

submitted by Mohammed Shaheen

submitted November 6, 2013

Supervisor / Advisor

Prof. Dr. Christian Theobalt Prof. Dr. Hans-Peter Seidel

Reviewers

Prof. Dr. Christian Theobalt Prof. Dr. Hans-Peter Seidel Dr. Robert Strzodka

#### Date of Colloquium:

5 November 2013

#### Dean:

Univ.-Prof. Dr. Mark Groves Faculty of Natural Sciences and Technology I Department of Computer Science Saarland University Saarbrücken, Germany

#### **Examination Board:**

Prof. Dr. Philipp Slusallek (Chair) Saarland University

Prof. Dr. Hans-Peter Seidel Max Planck Institut Informatik

Prof. Dr. Christian Theobalt Max Planck Institut Informatik

Dr. Robert Strzodka Nvidia Corporation

Dr. James Tompkin Max Planck Institut Informatik

#### Abstract

We are witnessing a fundamental paradigm shift in computer design. Memory has been and is becoming more hierarchical. Clock frequency is no longer crucial for performance. The on-chip core count is doubling rapidly. The quest for performance is growing. These facts have lead to complex computer systems which bestow high demands on scientific computing problems to achieve high performance.

Stencil computation is a frequent and important kernel that is affected by this complexity. Its importance stems from the wide variety of scientific and engineering applications that use it. The stencil kernel is a nearest-neighbor computation with low arithmetic intensity, thus it usually achieves only a tiny fraction of the peak performance when executed on modern computer systems. Fast on-chip memory modules were introduced as the hardware approach to alleviate the problem.

There are mainly three approaches to address the problem, cache aware, cache oblivious, and automatic loop transformation approaches. In this thesis, comprehensive cache aware and cache oblivious algorithms to optimize stencil computations on structured rectangular 2D and 3D grids are presented. Our algorithms observe the challenges for high performance in the previous approaches, devise solutions for them, and carefully balance the solution building blocks against each other.

The many-core systems put the scalability of memory access at stake which has lead to hierarchical main memory systems. This adds another locality challenge for performance. We tailor our frameworks to meet the new performance challenge on these architectures. Experiments are performed to evaluate the performance of our frameworks on synthetic as well as real world problems.

#### Abstract

Wir erleben gerade einen fundamentalen Paradigmenwechsel im Computer Design. Speicher wird immer mehr hierarchisch gegliedert. Die CPU Frequenz ist nicht mehr allein entscheidend für die Rechenleistung. Die Zahl der Kerne auf einem Chip verdoppelt sich in kurzen Zeitabständen. Das Verlangen nach mehr Leistung wächst dabei ungebremst. Dies hat komplexe Computersysteme zur Folge, die mit schwierigen Problemen aus dem Bereich des wissenschaftlichen Rechnens einhergehen um eine hohe Leistung zu erreichen.

Stencil Computation ist ein häufig eingesetzer und wichtiger Kernel, der durch diese Komplexität beeinflusst ist. Seine Bedeutung rührt von dessen zahlreichen wissenschaftlichen und ingenieurstechnischen Anwendungen. Der Stencil Kernel ist eine Nächster-Nachbar-Berechnung von niedriger artihmetischer Intensität. Deswegen erreicht es nur einen Bruchteil der möglichen Höchstleistung, wenn es auf modernen Computersystemen ausgeführt wird.

Es gibt im Wesentlichen drei Möglichkeiten dieses Problem anzugehen, und zwar durch cache-bewusste, cache-unbewusste und automatische Schleifentransformationsansätze. In dieser Doktorarbeit stellen wir vollständige cache-bewusste sowie cache-unbewusste Algorihtmen zur Optimierung von Stencilberechnungen auf einem strukturierten rechteckigen 2D und 3D Gitter. Unsere Algorithmen erfüllen die Erfordernisse für eien hohe Leistung und wiegen diese sorgfältig gegeneinander ab.

Das Problem der Skalierbarkeit von Speicherzugriffen führte zu hierarchischen Speichersystemen. Dies stellt eine weitere Herausforderung an die Leistung dar. Wir passen unser Framework dahingehend an, um mit dieser Herausforderung auf solchen Architekturen fertig zu werden. Wir führen Experimente durch, um die Leistung unseres Algorithmen auf syntethischen wie auch realen Problemen zu evaluieren.

#### Summary

Multi- and many-core architectures are rapidly becoming the norm in high performance computing. The trend towards many-core architectures exacerbates the problem because the increasing number of on-chip parallel cores renders an exponential growth in the compute capability whereas the system bandwidth increases only linearly. This shaped the so-called *memory wall* problem. Small, yet fast, on-chip memories called *caches* were introduced as the hardware approach to mitigate this problem.

At the core of the memory wall problem in scientific computing are iterative loops over discrete local operators. A typical representative is a stencil computation with constant weights or a sparse matrix vector product in case of variable weights. This computation pattern achieves only a tiny fraction of the peak computational performance due to its low arithmetic intensity.

In the literature, this problem has been approached from three perspectives. The first is cache-aware whereby the cache parameters are known to the algorithm at either compile or run time. The second is the cache-oblivious approach which, in contrast to the cacheaware approach, does not assume any knowledge about the cache parameters. The third looks at the problem as nested loops and uses loop transformation frameworks to optimize them.

All approaches revolve around the idea of cache locality optimization which exploits the fact that data is moved to the on-chip cache memories before any computation is done on it. Once data is on-chip, these approaches devise different techniques to perform as much computation on it as possible before it gets evicted from the cache. Cache locality can be improved by partitioning, also called *tiling*, the domain on which the stencil operator is applied into small groups called *tiles*. Tiles may also span the time which is the number of iterations in iterative stencil computations. However, as each iteration depends on the previous one, tiles must be skewed in the iteration space to form the so-called *time skewing*. The granularity of execution is the tile which means that the processor does not proceed to the next tile until it has finished executing the current tile. The advantage of running the stencil on tiles rather than the domain as a whole is that if the tiles are so small that they fit into the on-chip cache, the algorithm runs on data stored in the cache whose bandwidth is faster than the main memory bandwidth. Ongoing research is being conducted to design optimal tile parameters (shape and size) that are ideally also executable in parallel to cope with the multi- and many-core revolution.

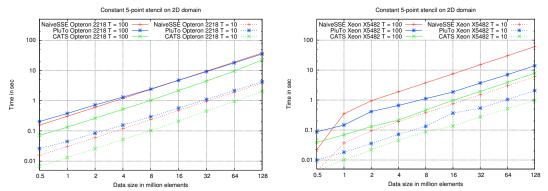

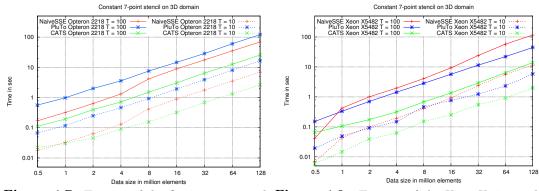

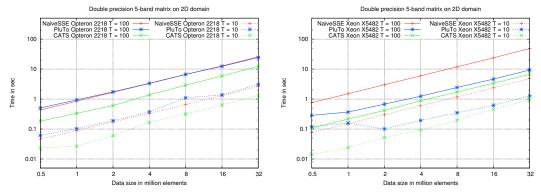

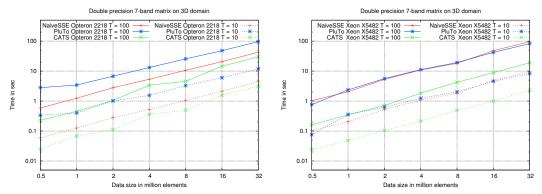

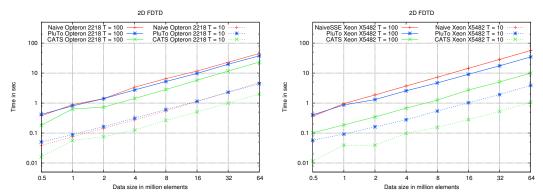

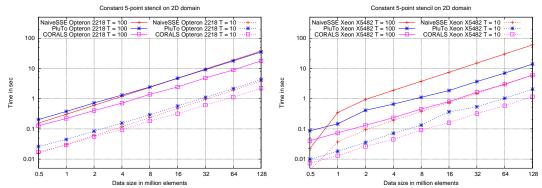

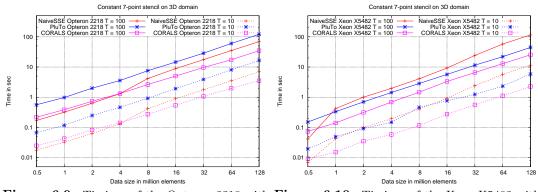

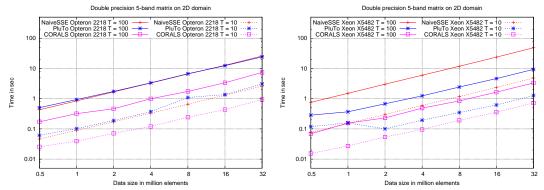

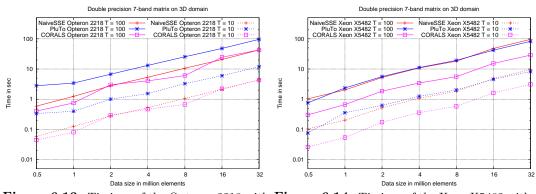

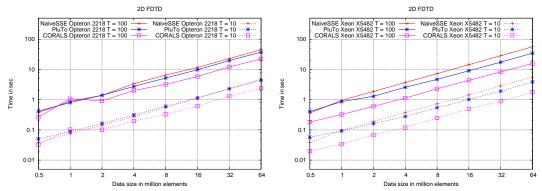

While different cache optimized approaches have been tried in the past, they have never been so successful. In this thesis, we pinpoint the deficiency of the state-of-the-art approaches and envision a set of cache-aware and cache-oblivious algorithms which avoids the deficiency. For example, on a quad-core Xeon X5482 3.2GHz system, a synthetic machine peak benchmark reaches 40.8 GFLOPS. On a large 3D domain of  $504^3$  double precision floating point and 100 iterations, a hand-vectorized single-threaded naive stencil implementation achieves 1.6 GFLOPS and there is no improvement in the multi-threaded version because the system memory bandwidth limits the performance. A state-of-art automatic loop transformation framework Pluto [7] achieves 1.9 GFLOPS for this stencil computation with four threads. In comparison, our schemes, called cache-aware time skewing (*CATS*) and cache-oblivious parallelograms in iterative stencil computations (*CORALS*) perform, in average, already at 5.3 GFLOPS with a single thread. Their performance soars to 13.0 GFLOPS with four threads. Furthermore, CORALS scores an excellent result on 2D domains by reaching 47% of the machine peak benchmark.

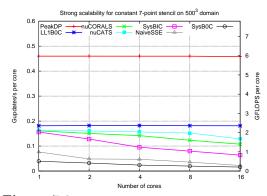

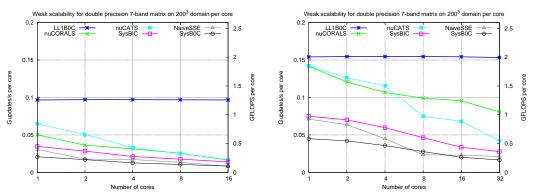

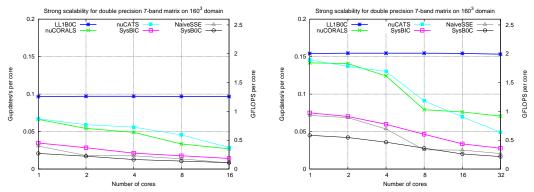

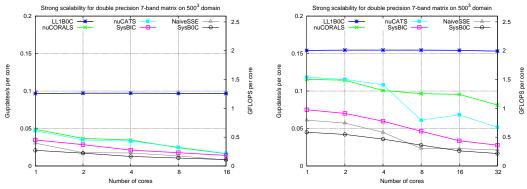

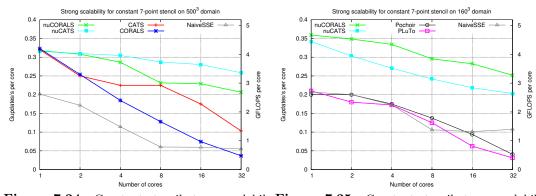

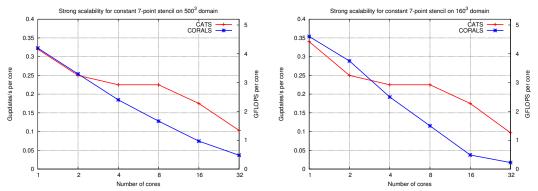

Efforts to improve the scalability of memory accesses in multiprocessing systems have introduced the non-uniform memory access (NUMA) memory systems whereby memory is physically distributed but logically shared. As such, in these architectures memory access time depends on the memory location relative to the processor, i.e. whether the memory location is in the local memory (memory modules directly connected to the processor) or in the remote memory (memory modules which are connected to other processors). The performance of our schemes, CATS and CORALS, may deteriorate depending on the amount of remote memory data that has to be updated by a certain core. This poses another challenge for performance on the new NUMA systems and schemes targeting these architectures have to explicitly account for a new performance aspect called *datato-core affinity*. To this end, we have extended CATS and CORALS to meet the new performance challenge. Our new schemes targeted at NUMA architectures which we call nuCATS and nuCORALS attain striking absolute performance and salient scalability on these architectures.

In summary, this thesis contributes to both cache-aware and cache oblivious-stencil computations. It has been perceived that high performance stencil computations are attainable solely by locality optimizations. While this is partially true as locality optimization yields the lion's share of performance, other factors such as parallelism and data-to-core affinity are essential for performance and their absence may adversely impact the performance gains expected from locality optimizations. This thesis formulates the requirements to achieve high performance stencil computations. It shows how failure to reckon with any of these requirements leads to schemes which hardly surpass the performance of an optimized naive scheme without any locality optimizations. We introduce two novel schemes which cater for all requirements simultaneously and achieve outstanding performance benefits from locality optimizations on stencil computations. We also show how to face the performance challenge posed by the NUMA memory systems in many-core systems and devise two new schemes that exhibit outstanding performance scaling.

#### Acknowledgements

This thesis would not come to be without the help and support of the following people. I would like to express my sincere gratitude to my supervisor Prof. Dr. Hans-Peter Seidel who gave me the great opportunity to work and do my research at the inspiring environment of the MPI Informatik and the Computer Graphics Group.

I would like to thank my direct mentor Dr. Robert Strzodka who sparked my interest in High Performance Computing. Robert continuously provided me with incitement and encouragement. On the other hand, I would like to thank my direct supervisor Prof. Dr. Christian Theobalt. Christian tirelessly provided me with all support, help, and feedback to finish this thesis with his group. I am indebted to both of them for their advice and guidance in my research.

I am grateful to Dr. Dawid Pajak for the long hours of fruitful discussions. Finally, I would like to thank my parents for their continuous support, and Ola, my wife, for her patience all the time.

# Contents

| 1        | Intr         | roduction                                        | 1  |

|----------|--------------|--------------------------------------------------|----|

|          | 1.1          | Problem Statement                                | 2  |

|          | 1.2          | Motivation                                       | 3  |

|          | 1.3          | Contributions                                    | 3  |

|          | 1.4          | Thesis Outline                                   | 5  |

|          | 1.5          | List of publications                             | 6  |

| <b>2</b> | Fun          | damentals                                        | 9  |

|          | 2.1          | Memory Hierarchy                                 | 9  |

|          | 2.2          | Locality Principle                               | 10 |

|          | 2.3          | Memory Configurations in Multiprocessing Systems | 11 |

|          | 2.4          | Stencil Computations                             | 12 |

|          | 2.5          | Space-time Traversals                            | 14 |

| 3        | Related Work |                                                  |    |

|          | 3.1          | Cache Aware Stencil Optimization                 | 19 |

|          | 3.2          | Cache Oblivious Stencil Optimization             | 21 |

|          | 3.3          | Loop nest Optimization                           | 22 |

| Ι | Iterative Stencil Computations for SMP Systems |                |                                    |           |

|---|------------------------------------------------|----------------|------------------------------------|-----------|

|   | 4                                              | Cac            | he Accurate Time Skewing           | <b>25</b> |

|   |                                                | 4.1            | Previous Work                      | 25        |

|   |                                                | 4.2            | Contributions                      | 26        |

|   |                                                | 4.3            | Cache Accurate Time Skewing (CATS) | 27        |

|   |                                                | 4.4            | Results                            | 35        |

|   |                                                | 4.5            | Conclusion                         | 42        |

|   | _                                              | _              |                                    |           |

|   | <b>5</b>                                       | $\mathbf{Per}$ | formance Modelling                 | 45        |

|                                  | 5.1 | Hardware Setup                               | 45 |

|----------------------------------|-----|----------------------------------------------|----|

|                                  | 5.2 | Software Setup                               | 46 |

|                                  | 5.3 | Naive and Time Skewed Stencil Computations   | 48 |

|                                  | 5.4 | Varying Cache Size                           | 50 |

|                                  | 5.5 | Performance Model                            | 52 |

|                                  | 5.6 | Model Evaluation                             | 54 |

|                                  | 5.7 | Conclusion                                   | 57 |

| 6 Cache Oblivious Parallelograms |     |                                              | 59 |

|                                  | 6.1 | Previous Work                                | 59 |

|                                  | 6.2 | The Cache Oblivious Parallelograms Algorithm | 60 |

|                                  | 6.3 | Results                                      | 69 |

|                                  | 6.4 | Conclusion                                   | 74 |

| II | Itera | e Stencil Computations for NUMA systems |    |  |

|----|-------|-----------------------------------------|----|--|

|    | 7 NU  | MA Aware Stencil Computations           | 79 |  |

|    | 7.1   | NUMA-aware CATS Scheme (nuCATS)         | 80 |  |

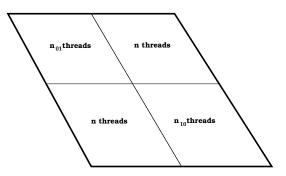

|    | 7.2   | NUMA-aware CORALS Scheme (nuCORALS)     | 81 |  |

|    | 7.3   | Results                                 | 84 |  |

|    | 7.4   | Conclusions                             | 99 |  |

| III | Application |                                         | 101   |

|-----|-------------|-----------------------------------------|-------|

| 8   | Opt         | tical Flow Estimation from RGBZ Cameras | 103   |

|     | 8.1         | Optical Flow from RGBZ Images           | . 104 |

|     | 8.2         | Minimisation                            | . 108 |

|     | 8.3         | Implementation                          | . 109 |

|     | 8.4         | Scene Flow Derivation                   | . 110 |

|     | 8.5         | Evaluation                              | . 110 |

|     | 8.6         | Conclusion                              | . 113 |

| 9   | Cor         | nclusion and Future Work                | 115   |

| в   | ibliog      | graphy                                  | 121   |

#### CONTENTS

### Chapter 1

## Introduction

Ever since the advent of the first general purpose electronic computer, computer technology has witnessed a continuous evolution. This evolution has been made possible by the advances in hardware and innovations in computer design. In 1945, the mathematician and computer scientist **John von Neumann** proposed a model for computer architecture called the stored program computer which assumes that an instruction fetch and a data operation cannot occur simultaneously because they share a common bus. Therefore, he proposed to use a single storage structure to hold both data and instructions. This is referred to as the Von Neumann bottleneck and often limits the performance of the system. Later on, Harvard Mark I proposed another architecture called Harvard architecture in which he suggested to separate storage and signal pathways for both data and instructions. Modern computer systems combine aspects from both architectures; on chip small, yet fast cache memories are provided between the processor and the main memory to circumvent the performance bottleneck of the Von Neumann architecture. These cache memories are often separate and have separate access pathways for data and instructions, the so-called Modified Harvard architecture. On the other hand, the Von Neumann architecture is used for the off chip main memory access.

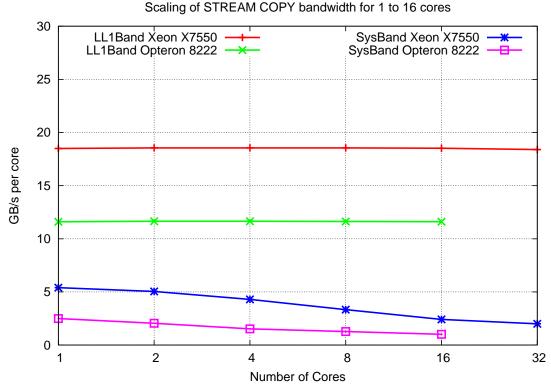

While clock frequencies of the processors increase, memories have not been able to keep pace with this increase. The growing disparity of speed between the processor and the off chip memory bandwidth is often referred to as the *memory wall* problem. In response, dual-, triple- and quad-channel memory interfaces have been introduced. They alleviate the problem temporarily but their scaling is too expensive to keep up with the exponentially growing number of cores. Data intensive applications suffer from severe slow down from this problem. In contrast to *system bandwidth* (off chip bandwidth), the aggregate cache bandwidth scales naturally with the number of cores if each core has a separate connection to its cache. Then doubling the number of cores also doubles the number of connections and thus the aggregate cache bandwidth. Ideally we would like data intensive applications to scale with the cache bandwidth rather than the system bandwidth. To this end, data intensive applications must utilize the *cache locality principle* as much as they can to break off the dependency on system bandwidth and scale with cache bandwidth. One basic computational pattern that suffers from the slow system bandwidth and can draw great performance benefits from the cache locality principle is *stencil computations*.

#### **1.1 Problem Statement**

Stencil computations are a class of kernels which update each point in a grid with a linear or non-linear combinations of its neighbor values, for example with a weighted subset of its neighbors. These kernels are usually applied many times (iterations) on the grid, therefore they are called *iterative stencil computations*. The number of neighbouring points involved in the update of a grid point including itself is called the *stencil size*. The distance between the updated grid point and the farthest grid point in the neighbourhood involved in the update is called the *stencil order*. Equation (1.1) shows a model stencil update in 3D. The equation is characterized by low arithmetic intensity (13 floating point operations) as the case for typical stencil computations. However; on a 504<sup>3</sup> grid and a Xeon X5482 machine, 4 threads and 100 iterations of this stencil problem achieve less than 4% of the computational stencil peak from registers. The reason is the memory wall problem. To analyze how the memory wall could have such an adverse impact on the performance, we first briefly explain how data processing happens in modern architectures.

$$X_{i,j,k}^{t+1} = c_1 \cdot X_{i-1,j,k}^t + c_2 \cdot X_{i,j-1,k}^t + c_3 \cdot X_{i,j,k-1}^t$$

$$+ c_4 \cdot X_{i+1,j,k}^t + c_5 \cdot X_{i,j+1,k}^t + c_6 \cdot X_{i,j,k+1}^t$$

$$+ c_0 \cdot X_{i,j,k}^t$$

$$(1.1)$$

Instructions fetched from instruction cache are executed by the processor until an instruction operating on data stored in the main memory is reached. The processor first checks the data cache for the data, and initiates a so-called *cache miss* if the needed data is not available in the cache. It temporarily stalls waiting for the larger and slower memories to provide the data which is then stored in the cache for the probability that it will be needed in the future (locality principle, see Chapter 2). The processor then resumes executing instructions. Given the discrepancy of speed between the processor and memory, the processor has to burn many cycles waiting for the cache to be refilled with the needed data which hurts the performance. The time needed to refill the cache with the needed data is called *cache miss penalty*. Iterative stencil computations on huge domains that do not fit into the cache undergo the same cache miss penalty for each iteration. For the very first iteration data is stored in the main memory and has to be fetched to the cache once needed. However, if the domain size is too big to fit entirely into the cache, the cache is overwritten already from the same iteration and data from the same address has to be fetched over and over again for each iteration which interprets the paradoxical stencil computations performance. In this thesis, we approach this problem from an algorithmic point of view, we observe the naive stencil performance on the most up-to-data architectures, analyze the problem and propose an algorithmic solution.

#### 1.2 Motivation

The motivation for this thesis is the importance of the stencil computation pattern. This importance stems from the importance of the stencil kernel which is a very frequent computational kernel arising in a variety of important scientific and engineering applications. The stencil kernel constitutes a significant fraction of the execution times of these applications. Such applications comprise partial differential equation solvers, image processing, computer vision, and simulations of climate, weather, and ocean. For example in the image processing domain, the well-known variational methods which often boil down to a system of equations that has to be solved numerically are a good example of stencil codes.

Although the problem has been thoroughly investigated and many approaches for alleviating it have been proposed, all proposed approaches are either complicated which limits their applicability or unsatisfactory in terms of the performance gains compared to what the state-of-art hardware can offer.

#### **1.3** Contributions

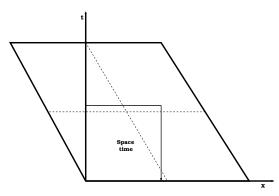

The idea behind all approaches for optimizing stencil computations is to group the domain (space) and the stencil iterations together to shape the *iteration space* or *space-time*. This iteration space is then partitioned into groups on which the stencil is applied. The partitioning and the resulting groups of space-time are referred to as *tiling* and *tiles*, respectively. The application of the stencil on the tiles happens in an atomic fashion, i.e. the whole tile (space and time) is executed by one processor before it can proceed to the next tile. In the literature, different tiling approaches are examined and they differ by tile size, tile shape, the way stencil is executed on each tile, or other parameters which will be explained later in this thesis. In Chapter 2, we explain how tiling is used to mitigate the stencil problem in more detail.

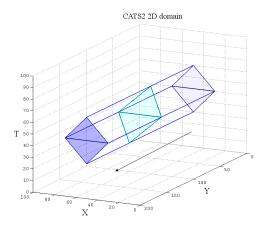

In this thesis, we propose a set of high performance stencil algorithms that perform beyond system bandwidth limitations. We approach the stencil problem from two perspectives. The first assumes that the cache parameters are available at execution time and use them to optimize the tile size so that the iterative stencil application incurs as few as possible cache misses. In the literature, such algorithms are usually referred to as *cache-aware* algorithms as opposed to cache-oblivious algorithms whereby no knowledge about cache parameters is assumed. The second perspective is the cache-oblivious approach. We present our cache-aware and cache-oblivious algorithms for stencil computations which are targeted at symmetric multiprocessing (SMP) in the first part (**Part I**) of this thesis. Symmetric multiprocessing systems (SMP) are characterized by the uniform main memory access, i.e. memory access time does not depend on the location of memory relative to the processor as opposed to the non-uniform memory access (NUMA) systems whereby memory access time depends on the location of memory relative to the processor. In the second part (**Part II**), an extension of the previous cache-aware and cache-oblivious algorithms to NUMA systems is presented. An important computer vision application which uses stencil computation at the core is presented in the third part (Part III). In particular, we present a novel high performance variational framework for scene flow estimation from one depth and one color cameras. In summary, our major contributions are:

- A cache-aware framework for iterative stencil computations called CATS [58, 60].

- A cache-oblivious framework for iterative stencil computations called CORALS [59].

- A performance model which predicts the execution time of the CATS scheme based on the number of incurred cache misses [57].

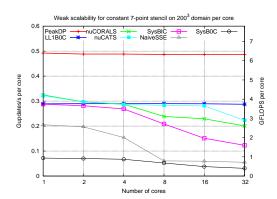

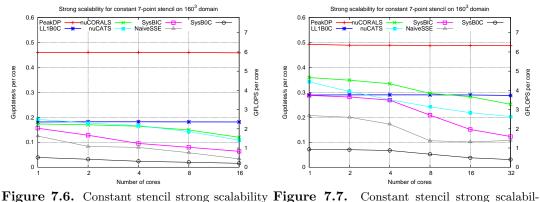

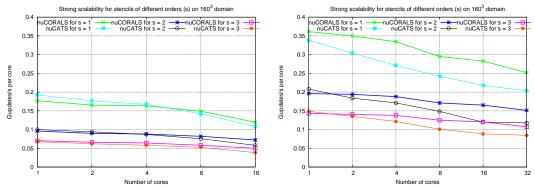

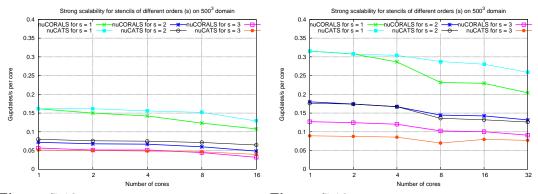

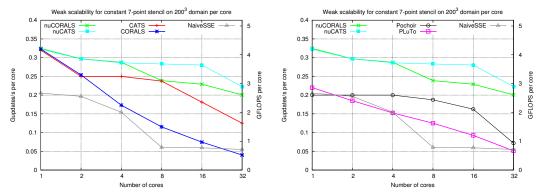

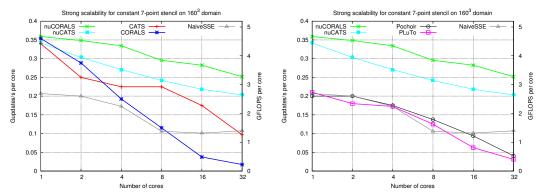

- Extensions of both CATS and CORALS (called nuCATS and nuCORALS, respectively) which exhibit weak as well as strong scalability when the memory is logically shared but physically distributed, the so called **NUMA** architectures [52].

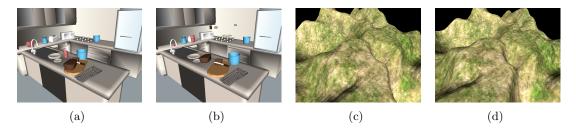

- A novel variational scene flow estimation from color and depth cameras that can benefit from the above algorithms.

The presented stencil algorithms can be applied to stencils of any order and size. Moreover, the stencil coefficients may vary across the domain, i.e., the schemes support also a product with a sparse banded matrix.

#### 1.3.1 Limitations

The presented algorithms are targeted at iterative stencil computations on structured rectangular grids. This means that high performance can be drawn from our algorithms

when the stencil is applied multiple times on the domain. Also, our algorithms can not be applied to stencil computations on non-structured grids or structured grids on arbitrary domain shapes (e.g. circular domains), although they can be easily extended to suit the latter type of domains.

#### 1.4 Thesis Outline

The rest of this thesis is structured as follows. Chapter 2 introduces the memory hierarchy which is regarded as the hardware approach to mitigate the memory wall problem. In this Chapter, we also distinguish two milestones in the memory architecture which influence the performance scalability of the memory bound algorithms in general. The first is symmetric multiprocessing (SMP) architectures and the second is the non-uniform memory access (NUMA) architectures. We also present the stencil problem and the previous efforts to approach the problem. In this context, we present *cache blocking, time skewing*, and *cache oblivious* stencil computation as the fundamental approaches to tackle the stencil problem. The rest of this thesis is organized into the following parts.

**Part I** is particularly devoted to our cache-aware and cache-oblivious stencil algorithms for symmetric multiprocessing systems (SMP). In Chapter 4, we propose a cache-aware framework for stencil computations called *cache accurate time skewing (CATS)*. The CATS scheme mitigates all drawbacks of the state-of-art approaches to optimize stencil computations on multidimensional domains and delivers high speedups over a recent code transformation tool and an optimized naive approach.

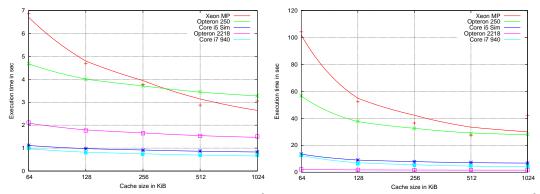

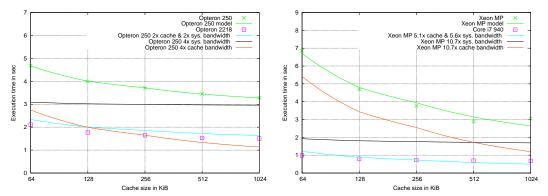

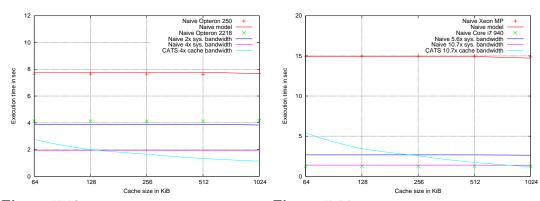

In Chapter 5, we present a performance model for the naive and the CATS schemes which uses the number of incurred cache misses to estimate the expected execution time on a certain machine. We use the model to examine the impact of scaling system and cache bandwidths on the naive and the CATS schemes for iterative stencil computations. We purport that scaling the cache bandwidth is more important to squeeze performance from time skewed iterative stencil computation algorithms.

Chapter 6 introduces our cache-oblivious parallelograms for iterative stencil computations (*CORALS*) algorithm. We show how CORALS caters for data locality, parallelism, and vectorization simultaneously in a cache-oblivious fashion. This high performance scheme comes at the cost of an irregular work-load distribution for which we introduce a tightly integrated load balancer to ensure a high utilization of all resources. At the time of publishing the related paper, CORALS delivered unprecedented outstanding performance which was not achievable with previous cache-oblivious stencil algorithms.

Part II is devoted to the variants of our cache-aware and cache-oblivious stencil algo-

rithms for non-uniform memory access (NUMA). In Chapter 7, we present *nuCATS* and *nuCORALS* as the NUMA variants of the CATS and CORALS schemes. We examine the scalability behavior of both CATS and CORALS on architectures with non uniform memory access (NUMA) memory systems, elicit the requirements for scalable high performance schemes on the NUMA architectures, and design variants for both CATS and CORALS that meet all these requirements. The presented comprehensive performance and scalability comparisons against various benchmarks derived from machine characteristics and a state-of-art code transformer and stencil compiler show the superiority of nuCATS and nuCORALS and emphasize the importance of considering the NUMA aspect as a very important one in any stencil code designated for scalable high performance computing.

**Part III** is devoted to applications. In particular we propose a novel variational framework for computing the scene flow from an RGB image sequence and the geometric information obtained from an active range sensor (Chapter 8).

We conclude this thesis in Chapter 9 and propose future directions for the research on this topic.

#### 1.5 List of publications

The work presented in this thesis has been published in the following papers:

- NUMA Aware Iterative Stencil Computations on Many-Core Systems Mohammed Shaheen, Robert Strzodka The 26th IEEE International Parallel & Distributed Processing Symposium (2012)

- Cache Accurate Time Skewing in Iterative Stencil Computations Robert Strzodka, Mohammed Shaheen, Dawid Pajak, Hans-Peter Seidel The 40th International Conference on Parallel Processing (2011)

- Impact of System and Cache Bandwidth on Stencil Computation Across Multiple Processor Generations Robert Strzodka, Mohammed Shaheen, Dawid Pajak

The 2nd Workshop on Applications for Multi and Many Core Processors (2011)

- Time Skewing Made Simple Robert Strzodka, Mohammed Shaheen, Dawid Pajak The 16th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming (PPoPP 2011)

- Cache Oblivious Parallelograms in Iterative Stencil Computations

#### 1.5. LIST OF PUBLICATIONS

Robert Strzodka, Mohammed Shaheen, Dawid Pajak, Hans-Peter Seidel The 24th ACM/SIGARCH International Conference on Supercomputing (2010)

• Overcoming Bandwidth Limitations in Visual Computing Robert Strzodka, Mohammed Shaheen, Dawid Pajak Visual Computing Research Conference (2009)

CHAPTER 1. INTRODUCTION

### Chapter 2

## **Fundamentals**

From vacuum tubes to transistors, and from integrated circuits to very large scale integration (VLSI) and ultra large scale integration (ULSI), computers have witnessed notable advances since their inception. In this chapter, we elaborate on some concepts and features of modern computer systems which are very important to understand this thesis. In particular we explain the hierarchical nature of computer memories nowadays. We also define the locality principle which is crucial for performance and discuss the two modern alternatives for organizing multiprocessing systems. The last Section is dedicated for stencil computations and the fundamental approaches to optimize their performance.

#### 2.1 Memory Hierarchy

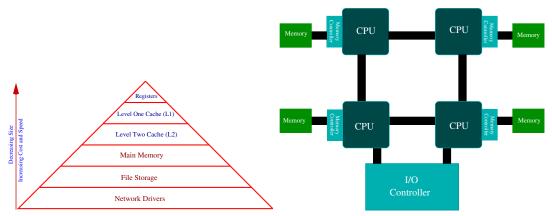

The memory system in nowadays machines is a hierarchy of memory modules with different costs, capacities, and speeds. The closer a memory module to the processor, the faster, smaller, and the more expensive it is. On the top of the hierarchy, reside the fastest memory modules which are called the *CPU registers*, see Figure 2.1. Registers typically hold the most frequently used data, e.g. loop variables. On the next level reside bigger memory modules called the *cache memories* which are located on-chip and hold a subset of the data and instructions stored in the relatively slow main memory. The cache itself is a hierarchy with typically two or three levels. Each cache level typically holds a subset of the data stored in the next level and is smaller in size. The main memory (RAM) is located off chip and serves as a staging area for data stored on the slow hard disks.

For programmers, understanding how data is moved up and down the hierarchy is crucial for writing high performance codes since well-written computer programs tend to access data stored at a certain level of the hierarchy more often than they access the next lower level. The idea here is to exploit the fact that data must be moved to the top of the

Figure 2.1. The Memory Hierarchy. Memory Figure 2.2. Non Uniform Memory Archispeed and cost increase while size decreases tecture (NUMA). Each processor has its own in the arrow direction. On chip memory is memory but can also access memories owned written in blue, and off chip memory is written by other processors. All processors share the in red. same address space.

hierarchy, typically registers and caches, before the first operation is performed on it. To this end, the program has to be structured in such a way that allows it to perform all required operations on the subset of data available in the cache. This relieves the processor from stalling each time it needs any data item from that subset and does not find it in the cache. This is called the *cache locality* principle and is discussed in detail in Section 2.2. Overall, the memory hierarchy serves as a large block of memory which provides data to the processor at the speed of the fast memory near the top of the hierarchy and at the cost of the cheap memory near the bottom of the hierarchy.

#### 2.2 Locality Principle

The cache memory is designed based on two concepts; the *spatial* and *temporal* locality of data access. *Spatial locality* principle implies that if some data are referenced at any point in time, it is likely that nearby data are also used in the computation. *Temporal locality* implies that data referenced now are likely to be used again in the future.

The idea here is that when a processor needs data at a certain memory address, it first checks the on chip memory, typically L1 cache, if data is not found there, a so-called L1 *cache miss* occurs and data is sought in L2 cache, and again if it is not found, L2 cache miss occurs, and data is sought in the higher cache levels (typically L3) if available before it is sought in the main memory and then higher levels of the hierarchy. Data are then moved up on the hierarchy. Typically a block whose size equals cache line size and contains the sought data is fetched to the cache. On one hand, fetching data in blocks satisfies the spatial locality principle. On the other hand, keeping data in the cache

satisfies the temporal locality principle. When data is sought and found in any cache level, a so called *cache hit* happens and there is no need to search further down in the hierarchy which adversely impacts the performance of the application. Our goal in this thesis is to improve the performance of stencil computations by maximizing the cache hit rate and minimizing the cache miss rate by maximizing data reuse once it is on chip (in cache).

Cache misses can be classified into

- Compulsory misses. The first access to data is always not in the cache, a compulsory miss occurs and a block containing the sought data must be brought into the cache.

- Capacity misses. The cache size is limited so it cannot contain all the blocks needed during execution of a program, capacity misses will occur due to blocks being evicted and fetched again later. The goal of the work presented in this thesis is to minimize this class of cache misses.

- Conflict misses. When two or more blocks of data frequently accessed by a program map to the same cache line, a so called conflict miss occurs and entails the so called *cache thrashing*. A lot of research is conducted to minimize this class of cache misses on both hardware and software levels; however, this is outside the scope of this thesis.

#### 2.3 Memory Configurations in Multiprocessing Systems

The memory in a cluster of microprocessors can be configured in one multiprocessing systems in two ways; non-uniform memory access (NUMA) and symmetric multiprocessing (SMP). In NUMA architectures [48], memory is physically distributed but logically shared meaning that each processor has its own local memory but also can access memory owned by other processors. Symmetric multiprocessing (SMP) systems, on the other hand, use a common bus to access a single shared main memory in the multiprocessing machine architectures. However, when new processors are added to the machine, this bus can get overloaded and thus becomes a performance bottleneck. Large multiprocessor systems use NUMA to alleviate the latter problem in which processors can access their local memories quickly compared to accessing memories owned by other processors which comes with interprocessor communication overhead. While this can significantly improve performance as long as data are localized, on the downside applications which need data movement between processors can suffer from severe performance slowdowns.

Maintaining coherent caches in NUMA systems has a notable overhead. The reason is that cache coherent non uniform memory access systems (ccNUMA) resort to interprocessor

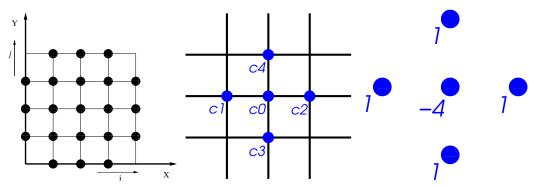

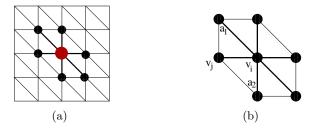

Figure 2.3. The 2D grid can Figure 2.4. A 2D 5-point Figure 2.5. The 2D stenbe used to discretize Poisson stencil with constant weights. cil resulting from discretizing Equation. Poisson equation.

communication between cache controllers to maintain a consistent image of the cached memory locations among the caches.

Each processor with its local memory is called a NUMA node. Data is moved on the bus between the clusters of NUMA nodes using scalable coherent interface (SCI) technology which maintains a coherent cache or consistent data in the caches of the different processors [62]. Although the NUMA nature of an architecture is transparent, programmers can effectively exploit the so called *first-touch allocation* [5] of operating systems to effectively optimize their programs for this type of architectures. First touch allocation means that a memory location is allocated in the local memory of the processor on which the process which has touched that memory location first is running. In other words, when a process running on processor x accesses for the first time (no other process has accessed it before) a variable, e.g. for initialization, a *page fault* [62] happens since the memory has not yet been allocated for the variable. The operating system allocated the memory on the local memory of processor x. We show how we benefit from this feature to improve the scalability of stencil computations in Chapter 7.

#### 2.4 Stencil Computations

As mentioned in the Introduction (Chapter 1), stencil computations are a class of iterative kernels which update each point in a grid with a weighted subset of its neighbours usually multiple times, and they are referred to as *iterative stencil computations*.

Stencil computations are ubiquitous in scientific computing primarily because the action of discretized local differential or integral operators can be expressed in this form. For example, using finite differences [41] to discretize the Poisson equation  $\Delta u = f$  on a 2D

#### 2.4. STENCIL COMPUTATIONS

grid yields for each node (i, j) on the grid (Figure 2.3)

$$u_{i-1,j} + u_{i+1,j} + u_{i,j-1} + u_{i,j+1} - 4u_{i,j} = h^2 f_{i,j}$$

$$(2.1)$$

This can be represented as a linear system of equations in the form

$$Au = b \tag{2.2}$$

Solving large PDEs and large linear equation systems in reasonable time requires iterative solvers, e.g. Gauss Seidel solvers [2]. Thus stencil computations are performed repeatedly for many iterations until convergence.

**Algorithm 1** Iterative stencil computations in 2D. The grid shown in Figure 2.4 has the dimensions XSIZE and YSIZE. The outer loop (t-loop) denotes the number of iterations needed for convergence in case of e.g. a numerical solver. c0-c4 are the stencil weights

```

\begin{array}{l} \mbox{Iterative_2D\_Stencil ()} \\ \{ & \mbox{for}(t=0;\,t<{\rm T};\,t{\rm ++}) \; \{ & \mbox{for}(j=0;\,j<{\rm YSIZE};\,j{\rm ++}) \; \{ & \mbox{for}(i=0;\,i<{\rm ZSIZE};\,i{\rm ++}) \; \{ & \mbox{A}(i,j)=c0^*{\rm A}(i,j)+c1^*{\rm A}(i{\rm -1},j)+c2^*{\rm A}(i,j{\rm -1})+c3^*{\rm A}(i,j{\rm -1})+c4^*{\rm A}(i,j{\rm +1}) & \mbox{} \} \} //{\rm x},{\rm y} & \mbox{} \} //{\rm t} \end{array}

```

Most often stencil computations are just a linear weighting of a small domain neighborhood, See Figures 2.4 and 2.5. In this case, the stencil computation represents a matrix vector products, with the position dependent stencil weights forming the rows of the matrix, and the discrete values of the domain (the grid) forming the vector. The arithmetic intensity [26] of such an operation is very low, with just one multiplication and addition per every vector and stencil component read, cf. Algorithm 1. Even if the stencil weights are constant and can be stored locally, there are still just two operations per every memory read, whereas even latest triple channel architectures prefer values of 8 and above, e.g. to balance computation and bandwidth on an Intel Core i7:  $4(\text{cores}) \cdot 3.2(\text{GHz}) \cdot 2(\text{SSE mad double}2)/25.6\text{GB/s} = 8\text{mad}/8\text{B}$  there should be 8 multiply and add (mad) operations for every double (8B). So only a non-linear stencil computations with many operations could prevent it from being memory bound.

When the discrete vector is so small that it fits into the processor's caches, the cache bandwidth becomes the limiting factor (unless there are not enough parallel compute units). However, this is not always the case since stencils in scientific computing typically operate on data much bigger than the cache capacity.

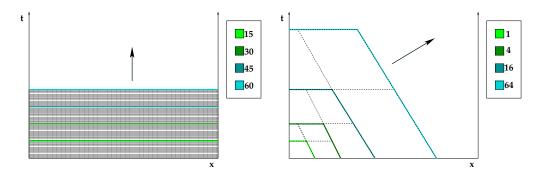

Figure 2.6. Naive space-time traversal. Figure 2.7. Hierarchical, cache oblivious The entire domain progresses one timestep space-time traversal. It computes on small after another. The evolution of the surfaces tiles but the execution order groups them separating the computed and not computed into bigger and bigger structures further impart of the space-time is shown. proving the volume to surface ratio.

#### 2.5 Space-time Traversals

This section describes the different space-time traversal algorithms. Given a discrete *d*dimensional spatial domain  $\Omega := \{1, \ldots, W_1\} \times \ldots \times \{1, \ldots, W_d\}$  with  $N := \#\Omega$  values we want to apply the stencil  $S : \{-s, \ldots, +s\}^d \times \Omega \to \mathbb{R}$  repeatedly to the entire domain *T*-times. So our space-time domain is given by  $\Omega \times \{0, \ldots, T\}$  with the initial values at  $\Omega \times \{0\}$  and boundary values at  $\partial\Omega \times \{0, \ldots, T\}$ ,  $\partial\Omega := \{0, W_1 + 1\} \times \ldots \times \{0, W_d + 1\}$ . Let us also define  $N_s$  as the number of non-zero elements in the stencil.

In the space-time  $\Omega \times \{0, \ldots, T\}$ , there are TN values to be computed, and each output values requires  $N_s$  input values, so in the worst case we will have  $TNN_s$  accesses to main memory. In this we assume a perfect cache of size Z with one word per cache line, full associativity and optimal replacement strategy, so a cache miss (and thus an access to main memory) occurs if and only if the required value is not present in the cache at that time.

If we access values from timestep t - 1 to compute values at timestep t then, irrespective of the scheme, we need to store two copies of  $\Omega$  during the stencil application. Some stencil computations like Gauss-Seidel [2], that use values from timestep t - 1 and t while computing timestep t, can be performed in-place with just one copy of  $\Omega$ , but we assume the general case here. A consequence of capturing the entire computation state in two copies of  $\Omega$  is, that if these two copies fit into the cache, then just N cache misses will be encountered no matter how large T is.

#### 2.5.1 Naive Stencil Computations

Given values at  $\Omega \times \{t-1\}$  for any  $t \in \{1, \ldots, T\}$ , we can compute values at the next timestep  $\Omega \times \{t\}$  with d nested spatial loops with index  $x_k, k \in \{1, \ldots, d\}$  running from 1 to  $W_k$  respectively. In practice, the inner most loop  $x_1$  corresponds to the unit stride direction, and the stride increases with every additional outer loop. Embedding all spatial loops in an outer time loop with index t running from 1 to T, we traverse the space-time in a naive way, progressing with the entire domain one timestep after another. Figure 2.6 visualizes this procedure.

In order to expand the computed part of the space-time without additional reads from main memory we would need to cache the entire surface between the computed and not computed part, i.e. the entire  $\Omega \times \{t\}$  would have to reside in cache, which is only possible for fairly small  $\Omega$ . However, partial data reuse during the spatial traversal of  $\Omega \times \{t\}$  occurs naturally whenever lower dimensional sub-structures of  $\Omega \times \{t-1\}$  of size  $W_1, W_1 \cdot W_2, \ldots, W_1 \cdots W_{d-1}$  stay in the cache after their first use, e.g. in 2D for a 3x3 stencil the line  $\{1, \ldots, W_1\} \times \{5\} \times \{t-1\}$  is needed for the computation of the three lines  $\{1, \ldots, W_1\} \times \{4, 5, 6\} \times \{t\}$ . Nevertheless, even with big caches this scheme performs poorly because the data reuse occurs only between data of adjacent timesteps.

#### 2.5.2 Cache Blocking

Cache blocking [21] is a cache utilization algorithm that attempts to minimize the cache misses of a program and hence enhance the performance by increasing the use of data already present in the cache. Cache blocking can yield a significant performance boost on computation patterns which are characterized by the large discrepancy between the floating point operations count and memory references needed. The basic idea here is to apply the computation on small blocks which are contiguous in memory. A loop nest which appears e.g. in matrix-matrix multiplication requires referencing memory locations that are not on the unit-stride dimension causing frequent cache misses when the array sizes exceed the cache size. Cache blocking restructures the loop nest so that the computation proceeds on small blocks which fit in the cache. Blocking variants and optimal blocking parameters have been a hot topic for research for many years.

Iterative stencil computations draw some benefit from cache blocking. Stencil computations are in essence a sparse matrix vector product. Cache blocking restructures computation to proceed on blocks of contiguous memory locations. However, in iterative stencil computations, only one iteration can be applied to each block since data at the boundary of each block depends on each other which limits the reuse from cache to the spatial locality. A technique to use the temporal locality and thus increase the overall reuse is called *Time Skewing*. In time skewing, multiple iterations can be applied to each block by skewing the boundary of each block in time which is explained in the Section 2.5.3.

#### 2.5.3 Time Skewing

When advancing certain blocks of the domain several stencil iterations ahead of the rest, we need to respect data dependencies induced by the form of the stencil. So called *time skewing* techniques have been described by Wolf [71], Song et al, [54] and Wonnacott [72]. Thereby, the time axis corresponds to the number of iterations the stencil is applied to the entire spatial domain, in general this is not the same as the time parameter of the PDE or other computational process in which the stencil is applied.

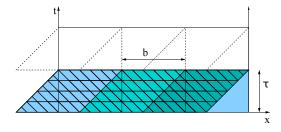

With this additional time axis we can form the space-time domain  $\Omega \times \{0, \ldots, T\}$ , where the data at  $\Omega \times \{0\}$  is given and the task is to compute a value for all remaining points in the space-time, see Figure 2.6. The idea is to look at the entire iteration space formed by the space and time, the *space-time*, and divide it into tiles that can be executed quickly in cache. To proceed to the next step locally without access to main memory, stencil computations require the neighbors of the previous iteration, therefore the tiles in the space-time are skewed with respect to the time axis, see Fig. 2.7. The execution inside the tile is very fast because these values are produced and consumed on-chip without the need for a main memory access. Only at the tile boundaries additional data must be brought into cache. If we know the L2 cache size in our CPU we can choose the tile size such that the base of the tile fits into the cache. To optimize for the memory hierarchy, we could further subdivide each tile into small tiles, whose bases fit into the L1 cache. All such parameters must be set conservatively, because any overestimation leads to cache thrashing and a severe performance penalty. In a multi-threaded environment, it is difficult to find the right parameters, since the available cache can be shared by different application threads and it is not clear which portion of the cache is available to the stencil computation at any given time. The tile dimensions form a large optimization space which can be explored empirically [32] and systematically [35, 49], whereby it makes a big difference if the exploration targets mainly data locality, or parallelism, or both equally.

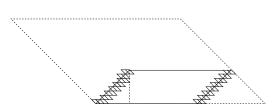

#### 2.5.4 Cache Oblivious Stencil Computation

A fourth approach is to use a hierarchical tiling that adapts automatically to the available cache size, which is thus named as *cache-oblivious* [17]. This can be achieved by iteratively tiling the space-time until small tiles are reached, see Figure 2.7. This hierarchical tiling has the advantage of optimizing for the whole memory hierarchy even without explicitly knowing its parameters (number of levels, size of each level,...etc). Despite the massive

cache miss reduction induced by cache-oblivious schemes, practically translating that into performance is fairly difficult. The programmer has to find a good tradeoff between the overhead associated with deepening the recursion tree (cache oblivious schemes are often implemented as a recursive algorithm) and the performance gains from running the scheme on data stored on deeper levels (closer to the processing elements) of the memory hierarchy.

### Chapter 3

## **Related Work**

Naive implementations of stencil computations suffer heavily from system bandwidth limitations. Most approaches to optimize stencil computations look at the problem from a cache locality perspective and therefore propose optimization techniques that can be classified into two categories. The first assumes that the cache parameters (cache size, cache hierarchy, and cache line size) are known beforehand, hence algorithms from this category are often referred to as *cache aware algorithms*. The second category is called *cache oblivious algorithms*. Although cache oblivious algorithms do not assume any knowledge about the cache parameters, in the asymptote, they use the cache as competently as the cache aware algorithms [19]. A more general approach, however, looks at the stencil as a special case of a loop nest with data dependencies and proposes loop nest optimizations accordingly. In this Chapter we review the efforts to optimize stencil computations in the literature and underline our work within the different approaches.

#### 3.1 Cache Aware Stencil Optimization

Cache blocking techniques have been developed to optimize for the spatial data locality. Lam et al. [36] study the impact of blocking on the performance of a matrix multiplication algorithm and conclude that the performance of blocked algorithms is highly dependent on the block and problem sizes. Kamil et al. [31] present recent empirical results from applying different blocking techniques in stencil computation algorithms. Frumkin and van der Wijngaart [20] have tight lower and upper bounds on the number of data loads. Dursun et al. [16] propose a multilevel parallelization framework for high order stencils based on domain decomposition and massage passing to exchange the subdomain boundaries on a cluster of CPUs. In [13], Datta et al. perform comprehensive stencil computations optimization and auto-tuning with both cache-aware and cache-oblivious approaches on a variety of state-of-the-art architectures, including GPUs.

Although recent results show large benefits in applying these techniques on multi-core architectures; however, no matter how efficiently we load the data into the caches, for data exceeding the cache size, we still read every vector component at least once per timestep from the main memory and for repeated applications of the stencil, this is far too much. To further reduce access to main memory, we need to exploit the outer loops that repeat the stencil computations over the same domain and make use of temporal locality. The reason is that spatial locality optimizations performed in the aforementioned works remain by construction bounded by the peak system bandwidth. In view of the exponentially growing discrepancy between peak system bandwidth and peak computational performance, this is a severe limitation for all current multi-core devices and even more so for future manycore devices. When advancing certain parts of the domain several stencil iterations ahead of the rest, we need to respect data dependencies induced by the form of the stencil. So called time skewing techniques have been described by Wolf [71], Song et al. [54], McCalpin and Wonnacott [40], and Wonnacott [72]. Thereby, the time axis corresponds to the number of iterations that the stencil is applied to the entire spatial domain, e.g., this can be the explicit time steps of a PDE solver, or the iterations of an iterative solver for linear equation systems. The general idea of time skewing is to tile the space-time into space-time tiles that can be executed with very few cache misses and ideally also in parallel. These requirements lead to skewed tiles in the space- time, see Chapter 2.

Common to all of the above approaches in case of a multi-dimensional domain, is a multidimensional tiling strategy: the time and multiple (not necessarily all) spatial dimensions are divided in order to form space-time tiles of approximately the same diameter in all divided dimensions. This minimizes the surface area to volume ratio of the space-time tiles and thus reduces cache misses. It is the best general strategy to traverse a space-time of unknown size [30]. However, knowing the typical cache size per core and domain sizes. In [58] and [60], we contribute an algorithm that does the exact opposite: we tile only one spatial dimension (resulting in enormous space-time tiles) and use the relatively large caches of nowadays cores to reduce the 2D or 3D problem to a 1D problem, where spatial tiling is not necessary and instead a wavefront traversal can be used. The resulting large space-time tiles can not only be traversed in a cache efficient fashion. They also allow for a SIMD friendly computation along the non-tiled unit stride dimension. On the other hand, while previous approaches resort to multilevel tiling to utilize the memory hierarchy, we only tile for the last cache level and thus maintain large tiles and wavefronts. Despite its simplicity, our scheme achieves superior results in comparison to the conventional multidimensional and multilevel tiling schemes, see Chapter 4.

Stencil optimization efforts were not only confined to CPUs, e.g. Williams et al. [68] and Datta et al. [14] investigate various stencil optimization techniques on the Cell BE.

Christen et al. [12] apply various optimization techniques to stencil computations arising in the biomedical simulations. The latter work targets the Cell BE and GPU architectures.

Kamil et al. [33] devise a microbenchmark called *Stanza Triad* to evaluate the impact of modern memory subsystem design on 3D stencil computations. In particular they evaluate the effectiveness of the prefetching engine in cache-based systems. They also develop a proxy for general stencil computations from which they derive a memory cost model for quantifying the performance of cache blocking stencil computations. In Chapter 5, we devise a performance model for naive and time skewing stencil codes based on the number of incurred cache misses. Our performance model provides useful insights into the most effective improvements for stencil computations on future processors.

#### 3.2 Cache Oblivious Stencil Optimization

Schemes that are able to exploit the memory hierarchy without explicitly knowing its size are first described in [47] and are called *cache oblivious algorithms*. Frigo and Strumpen [17] introduced a cache oblivious stencil scheme that divides the iteration space recursively into smaller and smaller space-time tiles and thus generates high temporal locality on all cache levels without knowing its sizes. The cache misses are greatly reduced leading to the desired reduction of system bandwidth requirements, however, the performance gains are relatively small in comparison to this reduction. Strumpen and Frigo [56] report a 2.2x speedup against the naive implementation of a 1D Lax-Wendroff kernel on a IBM Power5 system for periodic and constant boundary conditions after optimizing the software aspects of the scheme. After multifold optimizations and parameter tuning Kamil et al. [32] achieve a 4.17x speedup on the Power5 (15 GB/s theoretical peak bandwidth), 1.62x on an Itanium2 (6.4 GB/s) and 1.59x on an Opteron (5.2 GB/s) system for a 7-point stencil (two distinct coefficient values) on a  $256^3$  domain for periodic boundary conditions. However, for constant boundary conditions the optimized cache oblivious scheme is only faster on the Opteron achieving a 2x speedup at best. The compared naive code is optimized with ghost cells and compiled with optimization flags.

The above optimizations of the cache oblivious scheme are all directed at single-threaded execution. Frigo and Strumpen later analyzed multi-threaded cache oblivious algorithms [18]. One example deals with the cache misses of a 1D stencil code with parallel tile cuts. Blelloch et al. [6] discuss the construction of nested parallel algorithms with low cache complexity in the cache oblivious model for various algorithms including sparse matrix vector multiplication. However, these are mainly theoretical papers. In [59], we present a new cache oblivious scheme for iterative stencil computations that delivers the high speedups promised by the great cache miss reduction and clearly outperforms more general trans-

formation tools and optimized naive code. The most impressive results of our scheme are achieved in 2D. While a synthetic benchmark iterates over registers and performs 25.1 GFLOPS, our scheme iterates over a gigabyte large domain and performs 19.1 GFLOPS which are about 75% of the benchmark performance. This is an exceptionally outstanding performance as if the system bandwidth is hardly an issue.

#### 3.3 Loop nest Optimization

A more general approach to improve the temporal locality of iterative stencil computations is to see them as a special case of perfectly or imperfectly nested loops with data dependencies, see [53, 1, 24]. In this category, optimized and parallelized stencil kernels are automatically generated based on hardware models. Li and Song [38] present a framework for automatic stencil loops tiling based on memory cost analysis from which the tiling parameters (tile size and shape) that minimize the capacity misses are derived. Rivera and Tseng [51] develop a cost model for selecting tiling parameters and use it to find an optimal tiling transformation for 3D Jacobi kernels. Christen et al. [11] present an autotuner and a code generation framework for parallel stencil code based on domain specific description of the stencil kernel. The user of the framework can either choose from a set of predefined strategies or design a custom one to find optimal optimization on the machine in use. The polyhedral model provides an abstraction for valid transformations of nested loops. For an automatic source-to-source translation three steps are required: dependence analysis, transformations in the polyhedral model and code generation. Bondhugula et al. [7] present a complete system called PluTo [45] comprising all three steps. Given a source file it generates the optimized transformed code that can be compiled instead of the original source. Obviously, PluTo cannot successfully exploit data dependencies hidden behind complex index or pointer arithmetic, but it performs very well when arrays are allocated statically and data dependencies are expressed clearly. Other state-of-art tiling schemes for nested loops are HiTLoG [27, 34] and PrimeTile [46, 25]. Harton et al. [25] compare the performance of these tools. Recently, the Pochoir stencil compiler [63] uses the parallel cache oblivious algorithm [18] to optimize a stencil kernel specified in a domain specific stencil language. Although Pochoir succeeds in leveraging performance from the cache oblivious stencil algorithm of Frigo and Strumpen, the achieved performance is still poor and for certain problem size lies in the vicinity of a carefully optimized naive scheme.

## Part I

# Iterative Stencil Computations for Symmetric Multiprocessing Systems (SMP)

### Chapter 4

## Cache Accurate Time Skewing

In this Chapter, we present our cache aware time skewing scheme (CATS) for symmetric multiprocessing (SMP) memory systems. CATS breaks the memory wall for a certain class of iterative stencil computations. A stencil computation, even with constant weights, is a completely memory-bound algorithm. For example, for a large 3D domain of 500<sup>3</sup> doubles and 100 iterations on a quad-core Xeon X5482 3.2GHz system, a hand-vectorized and parallelized naive 7-point stencil implementation achieves only 1.4 GFLOPS because the system memory bandwidth limits the performance. Although many efforts have been undertaken to improve the performance of such nested loops, for large data sets they still lag far behind the performance of a synthetic machine peak benchmark. The state-of-art automatic locality optimizer PluTo [7] achieves 3.7 GFLOPS for the above stencil which constitutes less than 10% of the measured computational peak benchmark on the same machine (40.8 GFLOPS). CATS, on the other hand, achieves 13 GFLOPS which is 32% of the peak.

#### 4.1 Previous Work

For small discrete vectors that fit into the processor's caches, the cache bandwidth is the decisive factor of performance, but stencils in scientific computing typically operate on data much bigger than the cache capacity. Substantial work has been performed to optimize the data locality in such cases up to the point where tight lower and upper bounds on the number of data loads can be given [20]. Recent results show large benefits in applying these techniques on multi-core architectures [31]. But no matter how efficiently we load the data into the caches, for data exceeding the cache size, we still read every vector component at least once per timestep from the main memory and for repeated applications of the stencil, this is far too much. To further reduce access to main memory, we need to exploit

the outer loops that repeat the stencil computations over the same domain and make use of *temporal locality*. When advancing certain parts of the domain several stencil iterations ahead of the rest, we need to respect data dependencies induced by the form of the stencil. So called *time skewing* techniques have been described by Wolf [71], Song et al, [54] and Wonnacott [72]. Thereby, the time axis corresponds to the number of iterations that the stencil is applied to the entire spatial domain, e.g., this can be the explicit time steps of a PDE solver, or the iterations of an iterative solver for linear equation systems.

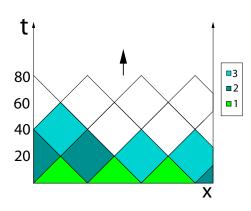

With this additional time axis we can form the space-time domain  $\Omega \times \{0, \ldots, T\}$ , where the data at  $\Omega \times \{0\}$  is given and the task is to compute a value for all remaining points in the space-time, see Figure 4.1. Now, the general idea of time skewing is to tile the space-time into space-time tiles that can be executed with very few cache misses and ideally also in parallel. These requirements lead to skewed tiles in the space-time, see Figure 4.2. The tile dimensions form a large optimization space which can be explored empirically [32, 14, 70] and systematically [35, 49, 43], whereby it makes a big difference if the exploration targets mainly data locality, or parallelism, or both equally. A more general approach for optimizing iterative stencil computations is to use a loop transformation and parallelization framework [22, 34, 7, 25, 4]. We compare our results against one of them in detail, namely PluTo [7], which is an easy-to-use fully automatic tool and a good indicator of the performance that can be achieved immediately on these nested loops without any further user interaction.

#### 4.2 Contributions

In case of a multi-dimensional domain, all schemes mentioned in Section 4.1 resort to the so called *multi-dimensional tiling* strategy: the time and multiple (not necessarily all) spatial dimensions are divided in order to form space-time tiles of approximately the same diameter in all divided dimensions, our scheme [60], in contrast, tiles only one spatial dimension (resulting in enormous space-time tiles) and use the relatively large caches of nowadays cores to reduce the 2D or 3D problem to a 1D problem, where spatial tiling is not necessary and instead a wavefront traversal can be used. *Multi-dimensional tiling* minimizes the surface area to volume ratio of the space-time tiles and thus reduces cache misses. It is the best general strategy to traverse a space-time of unknown size [30]. However, knowing the typical cache size of 128KiB–4MiB per core and domain sizes (100–1000)<sup>d</sup>, d = 2, 3, our scheme creates very large tiles which are much larger than the cache size and not only processes them in a cache efficient, but also a SIMD friendly manner.

Another difference is the treatment of the memory hierarchy. Previous approaches use a *multi-level tiling* strategy: they hierarchically subdivide the space-time tiles either explic-

itly or automatically with the idea that the basis of the sub-tiles will fit into a deeper cache level (e.g. L1) and thus the sub-tile will be processed faster. However, considering the concrete bandwidth and compute ratios, we explore the opposite direction of ignoring the memory hierarchy and instead maximizing the wavefront size in the last cache level (L2 in our case). The idea here is that large wavefronts maximize the number of space-time points that are processed on-chip in a *highly regular* fashion, while processing data from the L2 cache is not a big limitation.

We use a vectorized kernel for the actual computation as otherwise, the data processing could not keep up with the bandwidth of the L2 cache and the memory-bound stencil would become unnecessarily compute-bound. In other words, the vectorization ensures that the kernel remains memory-bound but cannot accelerate the execution beyond that.

We keep the rest of the scheme as simple as possible. We use a single form for all tiles and choose a minimalist parallelization approach: the threads are started once at the beginning and are persistent throughout the computation; furthermore the thread to tile assignment is known at compile-time leading to simple synchronization. This simplicity is of high importance since when benchmark performance is sought in applications, code simplicity is of great benefit to the compiler and hardware. Moreover, dynamic load-balancing is not necessary for tiles of equal size, and replacing barrier synchronization by tile-to-tile synchronization minimizes the idle time. As a result, our scheme achieves about 40% of the computational peak of a Xeon machine on 2D domains, whereas the state-of-art PluTo [7] achieves only 20% of this peak on the same 2D domain. This ratio falls off to 32% on a 3D domain of size 500<sup>3</sup>; however, it is still clearly superior to the performance of PluTo which exhibits a sharper fall off achieving only less than 10% of the peak.

### 4.3 Cache Accurate Time Skewing (CATS)

This section describes our new cache accurate time skewing schemes in comparison to the naive scheme. We first describe some specific variants of CATS and then explain how they combine to give the general CATS scheme.

On a discrete *d*-dimensional spatial domain  $\Omega := \{1, \ldots, W_1\} \times \ldots \times \{1, \ldots, W_d\}$  with  $N := \#\Omega$  values we want to apply a stencil  $S : \Omega \times \{-s, \ldots, +s\}^d \to \mathbb{R}$  of order *s* repeatedly to the entire domain *T*-times. In case of a constant stencil, *S* does not depend on  $\Omega$  and has a certain number of non-zero values  $N_S := \#S$ , otherwise we assume that the stencil is position dependent,  $S(x) : \{-s, \ldots, +s\}^d \to \mathbb{R}, x \in \Omega$  and has the same number of non-zero values  $N_S$  for every position, and  $N \cdot N_S$  values overall.

Our space-time domain is given by  $\Omega \times \{0, \ldots, T\}$  with the initial values at  $\Omega \times \{0\}$  and

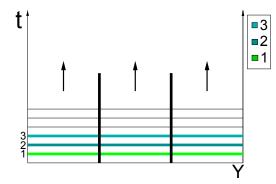

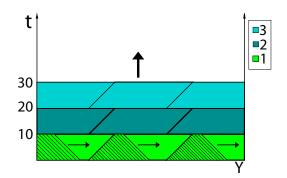

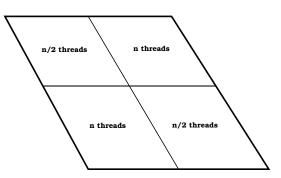

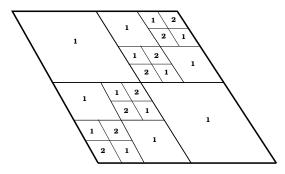

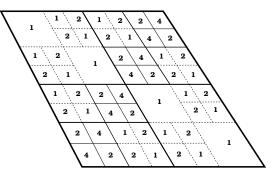

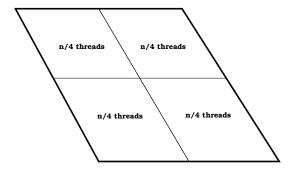

Figure 4.1. Naive space-time traversal in parallel with three threads, cf. Alg. 2. Regions of the same color are operated on in parallel, synchronization takes place before starting a different color region. The entire domain progresses one timestep after another in sync in the direction of the arrows. X-dimension goes into the page.

Figure 4.2. Cache accurate time skewing with one skewing dimension (CATS1) in parallel with three threads, cf. Alg. 3. Regions of the same color are operated on in parallel, synchronization takes place before starting a different color region. The fine lines show the consecutive wavefront positions and the arrows the traversal direction in each parallelogram. X-dimension goes into the page.

boundary values at  $\partial\Omega \times \{0, \ldots, T\}$ ,  $\partial\Omega := \{0, W_1+1\} \times \ldots \times \{0, W_d+1\}$ . In the space-time  $\Omega \times \{0, \ldots, T\}$  there are TN values to be computed, and each output value requires  $N_S$  input values. So in case of a constant stencil we perform  $TNN_S$  reads and TN writes; in case of a variable stencil (banded matrix) we perform  $2TNN_S$  reads and TN writes.

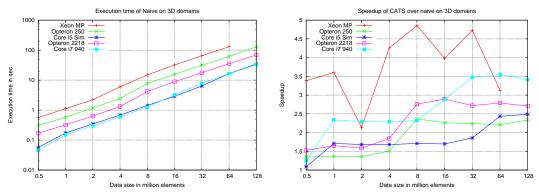

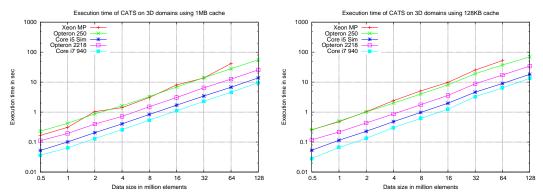

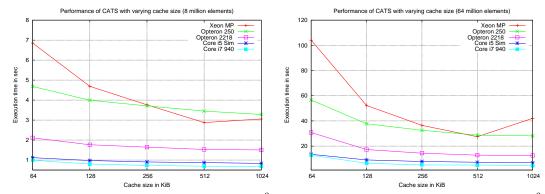

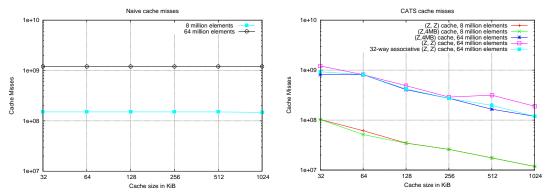

If we access values from timestep t-1 to compute values at timestep t then, irrespective of the scheme, we need to store two copies of  $\Omega$  during the stencil application. Some stencil computations like Gauss-Seidel, that use values from timestep t-1 and t while computing timestep t, can be performed in-place with just one copy of  $\Omega$ . If these one/two copies of  $\Omega$  fit into the cache, then all reads and writes will happen in the cache no matter how large T is. The naive scheme performs much better in this case, as can be seen for the 0.5 million elements case in the Figures. 4.6 and 4.8.

### 4.3.1 No Skewing - NaiveSSE Scheme

The naive stencil implementation has no data reuse between different iterations. The entire spatial domain advances one timestep after another, see Figure 4.1 and Alg. 2. The outermost spatial loop is parallelized with multiple threads, whereby each thread operates on one tile of the domain. The tiles are of the same size so the threads can be synchronized with little overhead after each timestep. The innermost spatial loop (unit stride dimension) is hand-vectorized with SSE2 intrinsics.

Algorithm 2 The naive scheme for iterative stencil computations in 2D. The spatial domain is cut along the y-dimension into tiles for parallel execution and ystart(tid), yend(tid) are the tile bounds in dependence on the thread ID tid.

```

naive_2D () {

for(t = 0; t < T; t++) {

for(y = ystart(tid); y < yend(tid); y++) { // parallelized

for(x = 0; x < WIDTH; x++) { // vectorized

apply 2D stencil at position (x,y,t);

}}//x,y

synchronize threads;

}//t

}

```

### 4.3.2 Skewing One Dimension - CATS1 Scheme

Algorithm 3 CATS1 for iterative stencil computations in 2D. The loop bounds ystart(tid), yend(tid) represent the extent of the tile (parallelogram) along the traversal dimension y. The loop bounds tstart(ts,y), tend(ts,y) represent the extent of the wavefront along the dimension t within the tile, see Figure 4.2.

```

CATS1_2D()

{

compute height T_Z from cache size (Eq. 4.1);

for(ts = 0; ts < T/T_Z; ts++) {

for(y = ystart(tid); y < yend(tid); y++) { // parallelized

if(y == ystart(tid+1)) {

wait for (tid+1) to finish its left tile border;

for(t = tstart(ts,y); t < tend(ts,y); t++) {

for(x = 0; x < WIDTH; x++) {

// vectorized

apply 2D stencil at position (x,y-t,t);

}//x

}//t

}//y

synchronize threads;

}//ts

}

```

The general idea behind time skewing schemes is to compute multiple timesteps at once in certain parts of the domain thus exploiting the temporal producer-consumer locality. For this purpose we tile one spatial dimension. The plane formed by the chosen spatial dimension and the time dimension is divided into space-time tiles, see Figure 4.2. The tiles are skewed to respect the temporal data dependencies induced by the stencil. Processing within the space-time tile has high temporal locality, while data at the tile borders, in general, has to be reloaded from main memory. Skewed tile borders require more data transfer than straight tile borders. The main decision is on the form of the tiles, aiming for maximal temporal locality and parallel processing of tiles. We use parallelogram tiles with split-tiling and wavefront processing (Figure 4.2).

These ideas have been described for multiple processors instead of cores already at the onset of time skewing methods by Wonnacott [72], but even in CATS1 we use them differently for multi-dimensional domains. In particular, we show that multi-dimensional tiling of multi-dimensional domains is not necessary. Instead of diagonal wavefronts, we consider axis-aligned wavefronts, and our tile placement is also different. The pipelined temporal blocking by Wittmann et al. [70] and Wellein et al. [67] can also be seen as a variant of space-time wavefront processing. However, they use the term 'wavefront' completely differently, describing the parallelization along the time axis, which benefits from shared caches between multiple threads. This type of 'wavefront' does not exist in our scheme, because we use a different parallelization approach that does not rely on shared caches; instead we construct large space-time wavefronts (using Wonnacott's space-time notion of a wavefront) for the purpose of the data locality maximization.

In wavefront processing we sweep with a skewed space-time surface (the *wavefront*) through the tile along a designated *traversal dimension* (see the arrows in Figure 4.2), maintaining a certain number of the most recent wavefronts in the cache. The computation takes place at the wavefront reusing the data from the previous wavefronts. New data must only be fetched from main memory at the tile borders. For a stencil width of 2s+1 in the traversal dimension, 2s wavefronts plus some temporary variables must reside in an ideal cache for perfect data reuse, but because of limited cache associativity and cache line granularity, a certain value  $C_S \in (2s, 2s+1]$  is used in practice, e.g., Wonnacott [72] uses the pessimistic  $C_S:= 3$  for a 3-wide stencil, we conservatively choose  $C_S:= 2s + 0.8$  after a cache miss analysis.

The main advantage of wavefront processing is that the tiles can be much bigger than the cache, because only  $C_S$  wavefronts must reside in the cache for a perfect producerconsumer locality within the tile. One driving idea behind our cache accurate time skewing schemes is to radically maximize the wavefront size at the expense of any other locality optimizations. In case of one dimensional skewing, CATS1 maximizes the wavefront size such that  $C_S$  wavefronts barely fit into the private L2 cache of one thread. Let Z be the size of the private L2 cache and  $W_{\text{max}}$  the size of the largest domain dimension, the one to be traversed, then the size of our wavefront is  $T_Z N/W_{\text{max}}$  and we can compute the maximal temporal extent of our tile  $T_Z$  in dependence on Z as

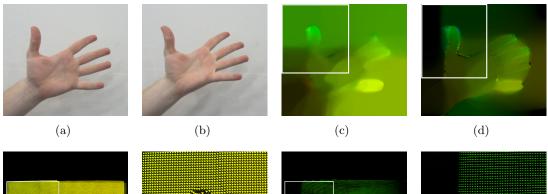

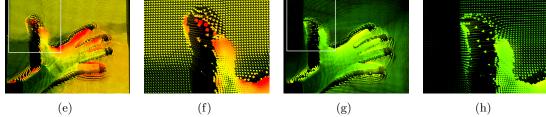

$$T_Z := \left\lfloor ZW_{\max} / \left( C_S N \right) \right\rfloor. \tag{4.1}$$